实验一 与非门与计数器

一、实验目的

1.熟悉实验箱、示波器和proteus软件,理解芯片和元件的作用与关系;

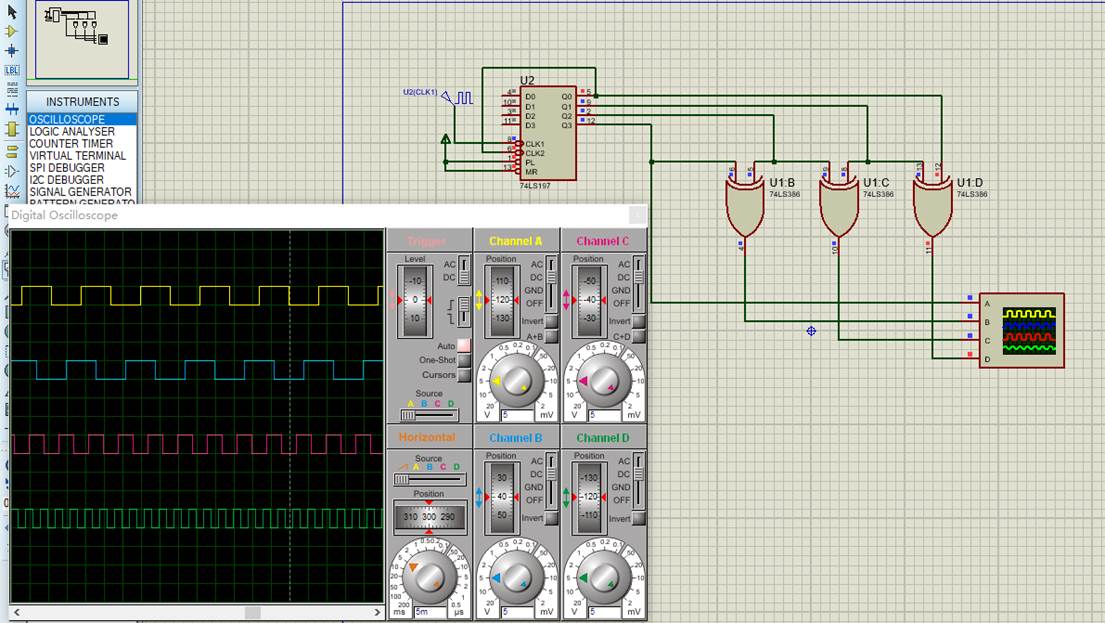

2.用74LS197完成计数器,用74LS00完成与非门,观察输入输出的波形。

二、实验要求

系统输入:时钟脉冲;

系统输出:七段数码管的显示和发光二极管;

系统功能:与非门功能测试,八进制计数器。

三、实验内容

1.与非门静态测试:

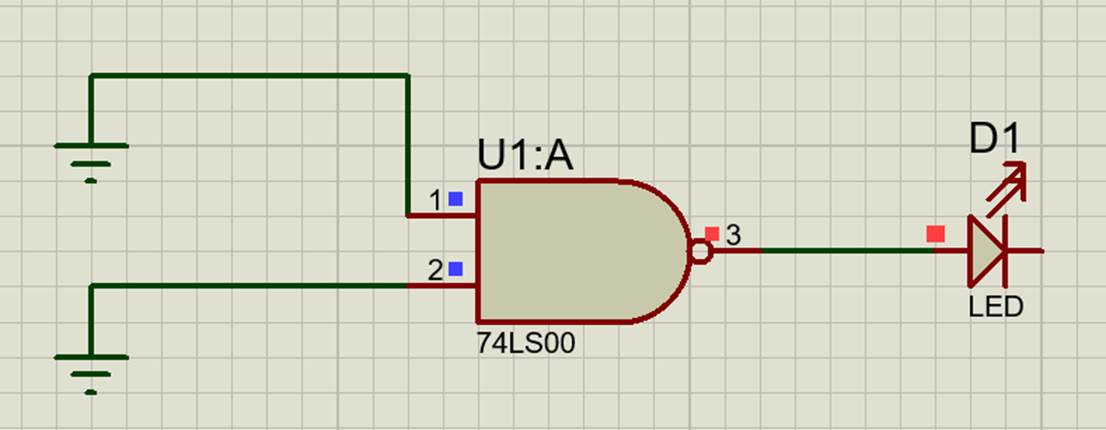

74LS00作为与非门,输入端接入高电位或低电位,输出端接入LED,通过观察LED的亮暗程度,完成真值表。

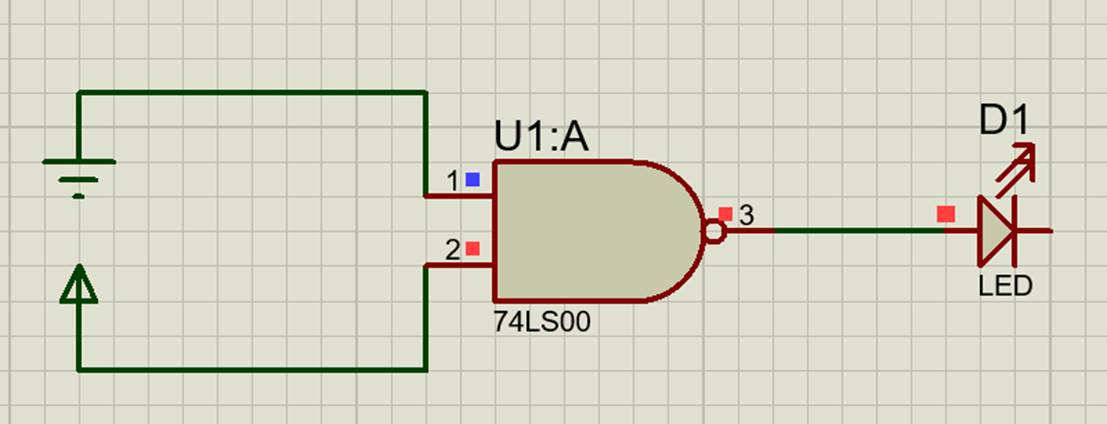

(1)两个高电平输入时:

线路图:

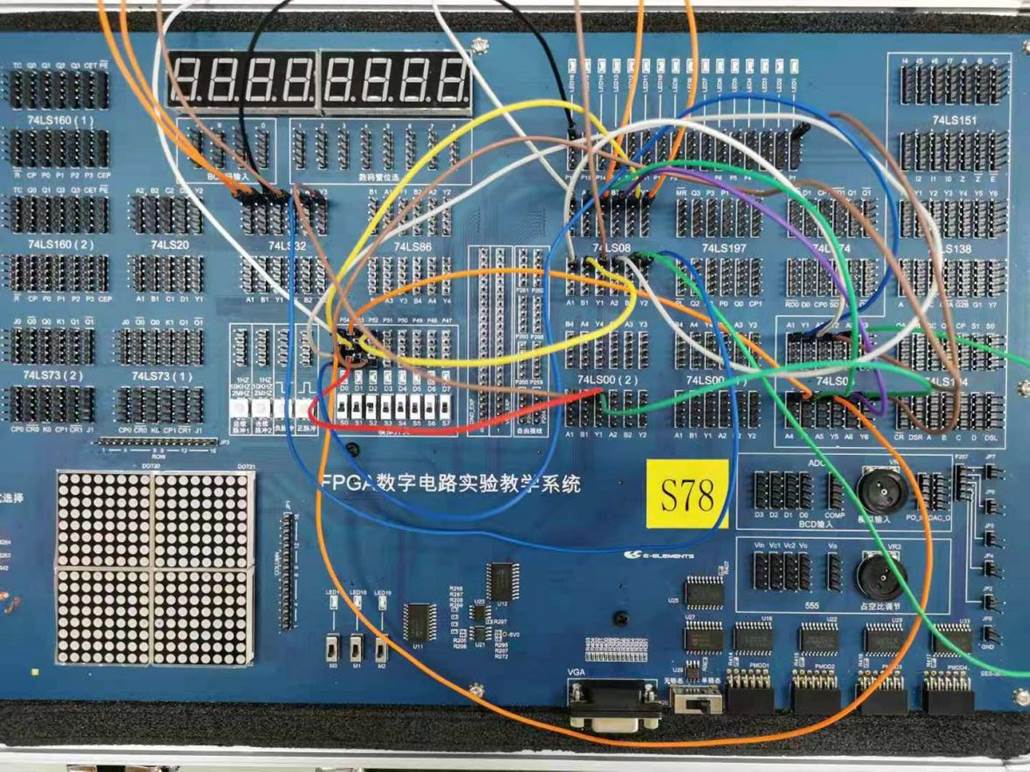

实验图:

实验现象:两个输入都为HIGH时,输出为LOW,LED发光。

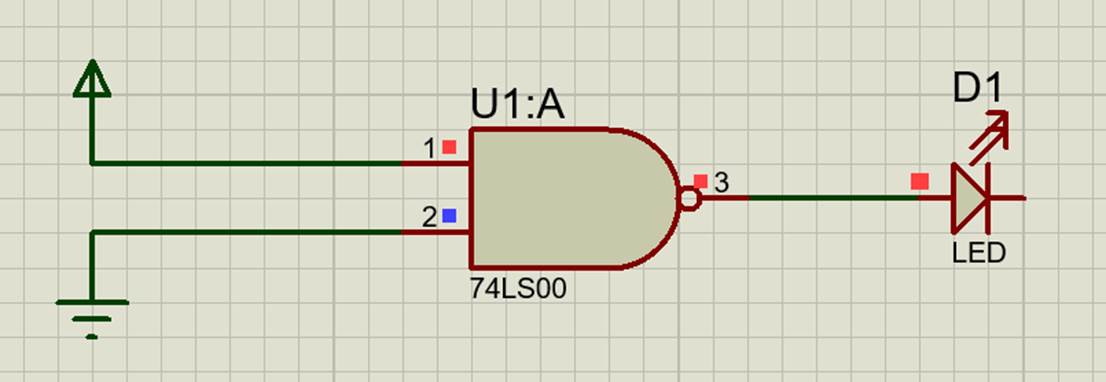

(2)一个高电平输入,一个低电平输入时:

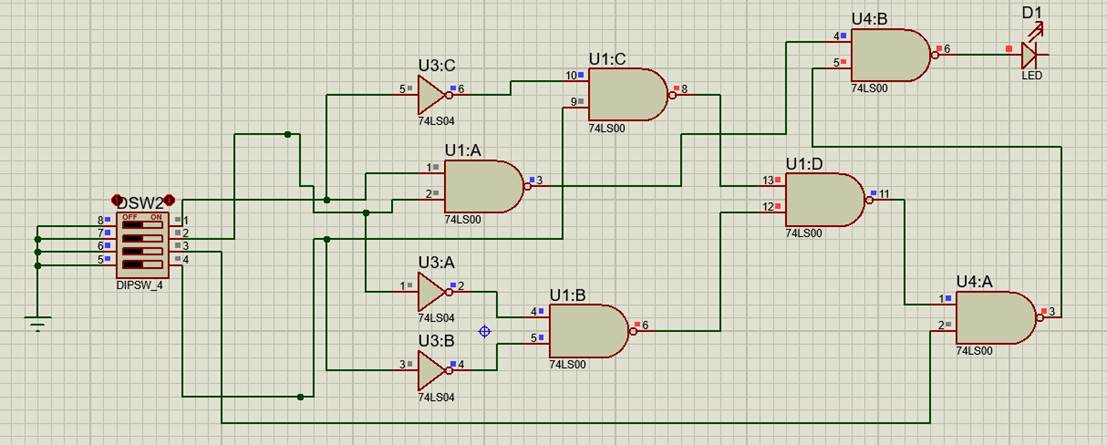

电路图:

实验图:

实验现象:一个输入为HIGH,另一个为LOW时,输出为HIGH

(3)两个低电平输入时:

电路图:

实验图:

实验现象:两个输入都为LOW时,输出为HIGH

真值表:

| 输入信号1 | 输入信号2 | 输出信号 |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

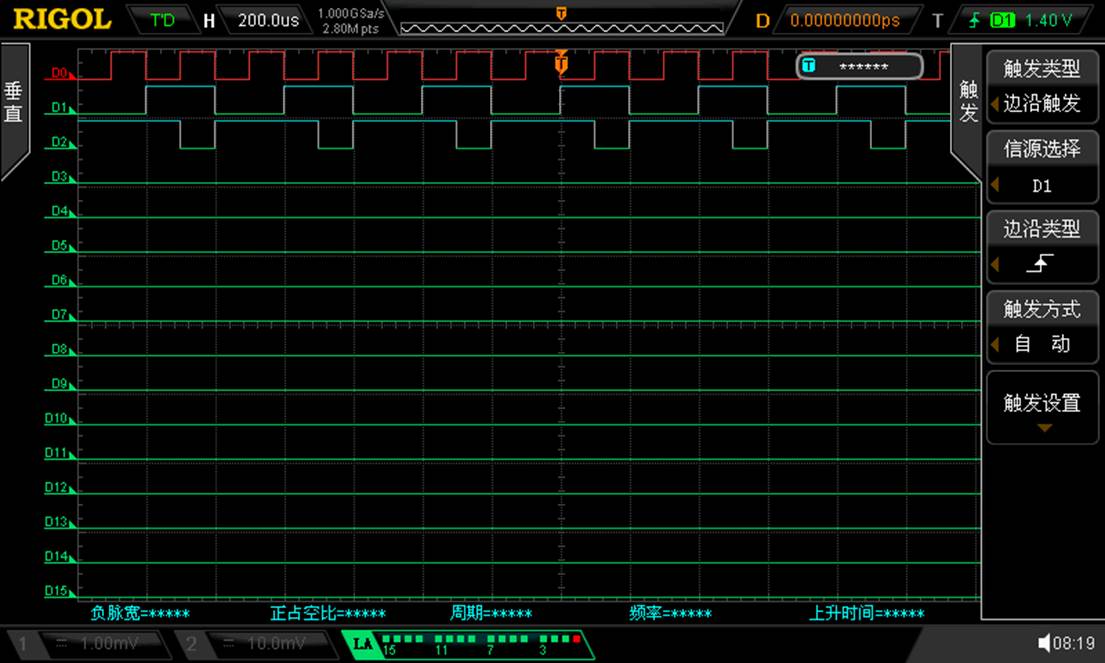

2.与非门动态测试:

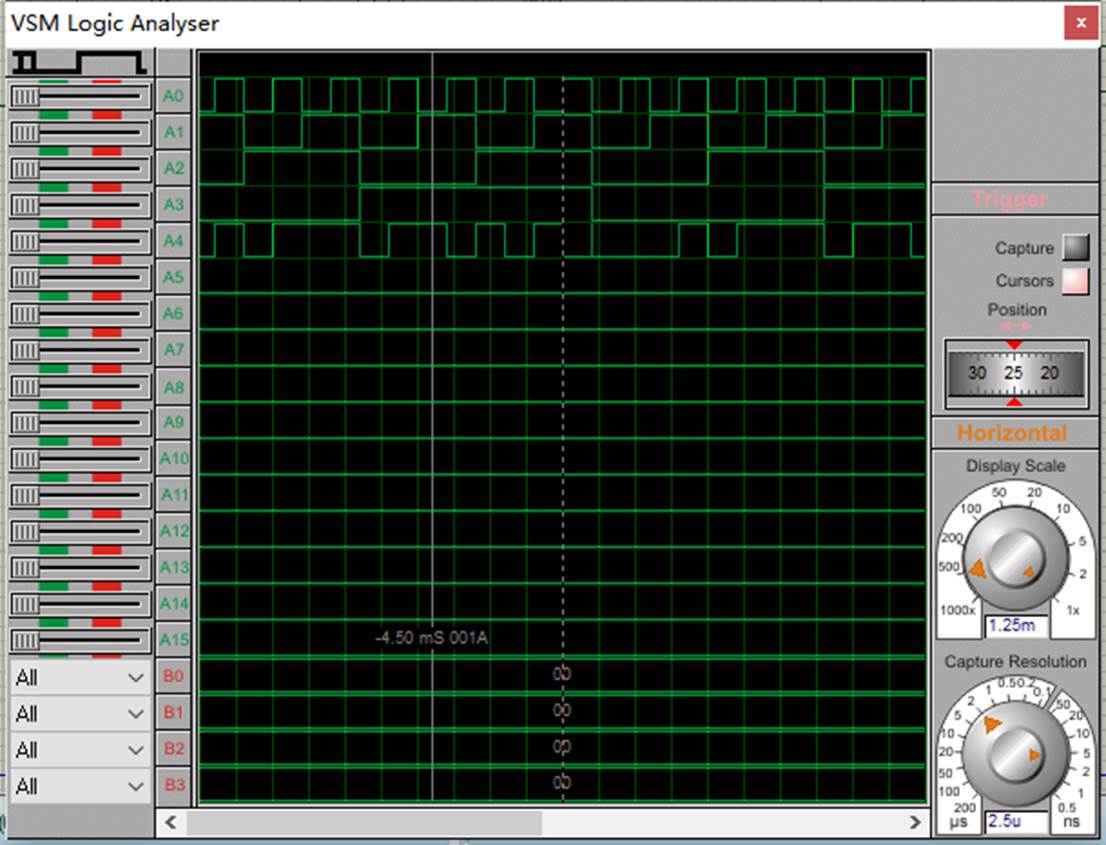

电路图:

实验图:

实验现象:第一、二条曲线是输入端信号,第三条曲线是输入信号的与非运算结果。

实验二 延迟与竞争冒险

一、实验目的

1.观察器件延迟现象,了解竞争冒险现象及其原因;

2.观察竞争冒险产生的尖峰脉冲现象;

3.学习如何消除竞争冒险。

二、实验要求

系统输入:时钟脉冲,模拟开关;

系统输出:示波器;

系统功能:产生尖峰脉冲现象并消除。

三、实验内容

1.器件延迟现象:

(1)Y=AA’:

Y=AA’是Y恒为0的逻辑表达式,可采用与门与非门连接电路(电路图连接方式),实际上也可采用74LS00作为与非门进行连接(实际实验连接方式):A跟A’做与非运算后结果再取非。

理论是Y的值恒为0,实际上由于非门的延迟产生了竞争冒险,出现了尖峰脉冲现象。

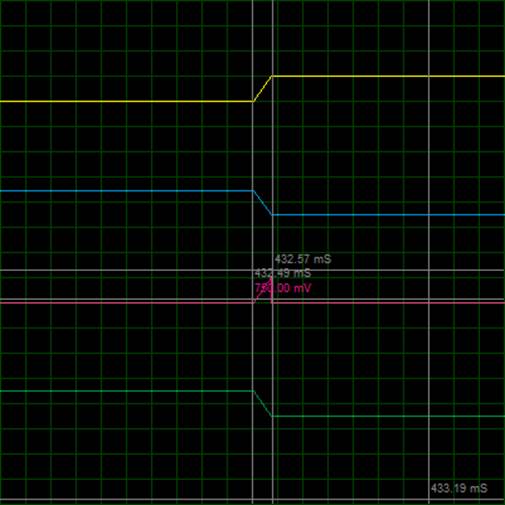

线路图:

实验图:

实验现象:在输出端得到稳定的输出前,出现了形状是宽度仅为时差的窄脉冲。

测量结果:

一个非门的延迟:432.57-432.49=0.08ms

毛刺的幅度:5V

(2)Y=A+A’:

Y=A+A’是Y恒为1的逻辑表达式,可采用或门与非门连接电路,在电路图中,一个非门产生的现象并不明显,故采用了三个非门观察现象。实际中,一个非门即可在示波器中产生尖峰脉冲现象。

理论是Y的值恒为1,实际上由于非门的延迟产生了竞争冒险,出现了尖峰脉冲现象。

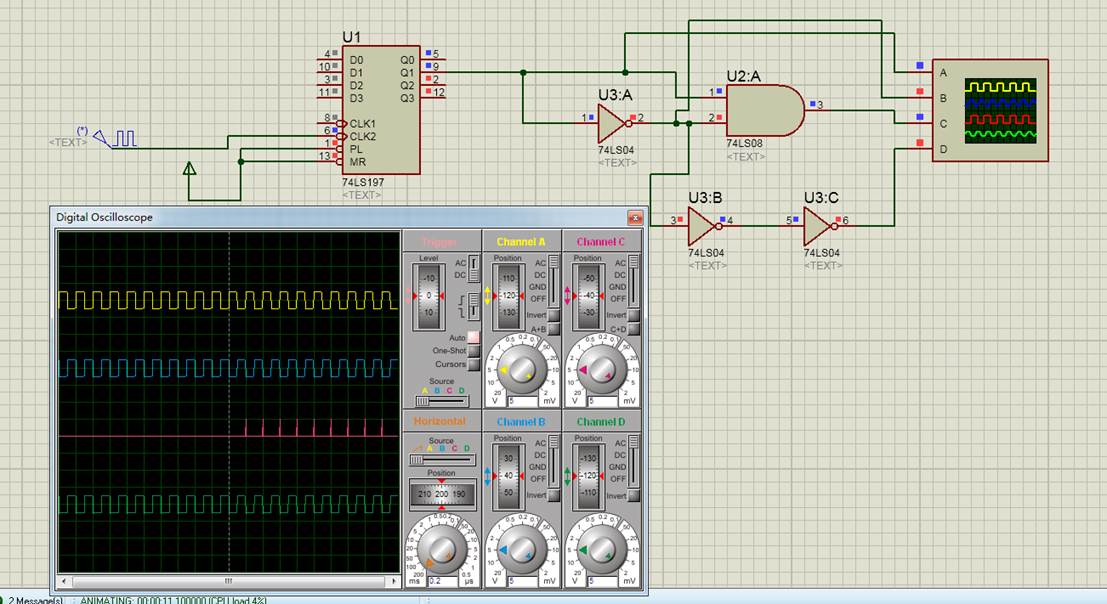

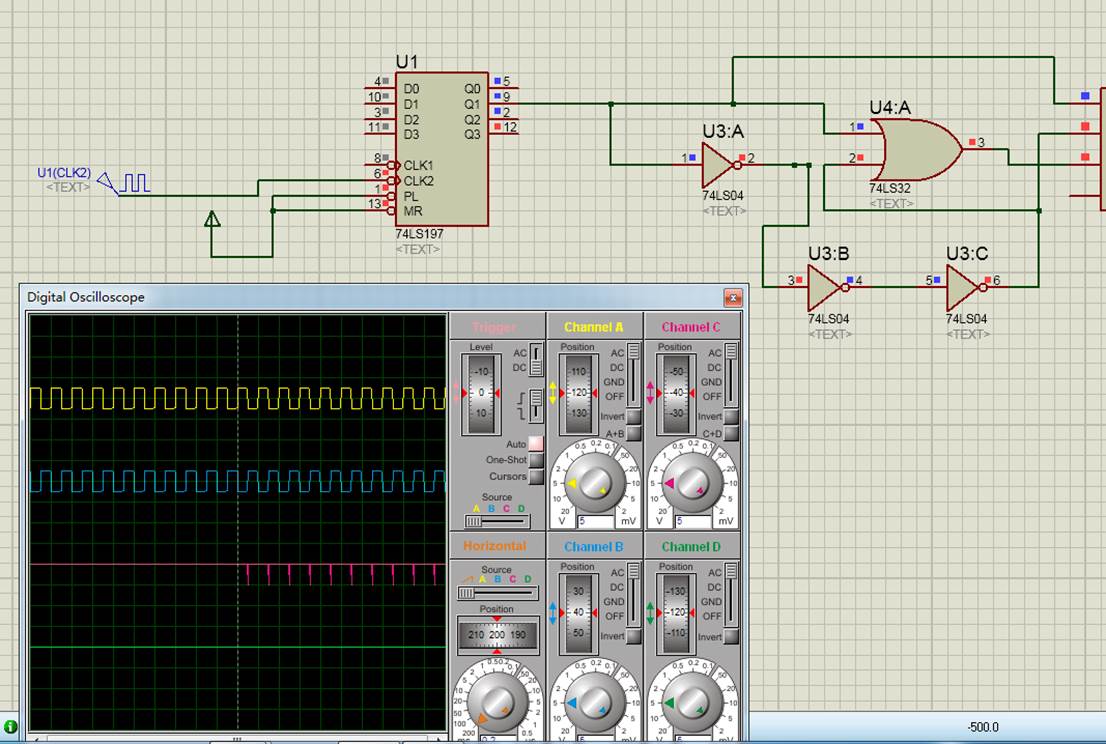

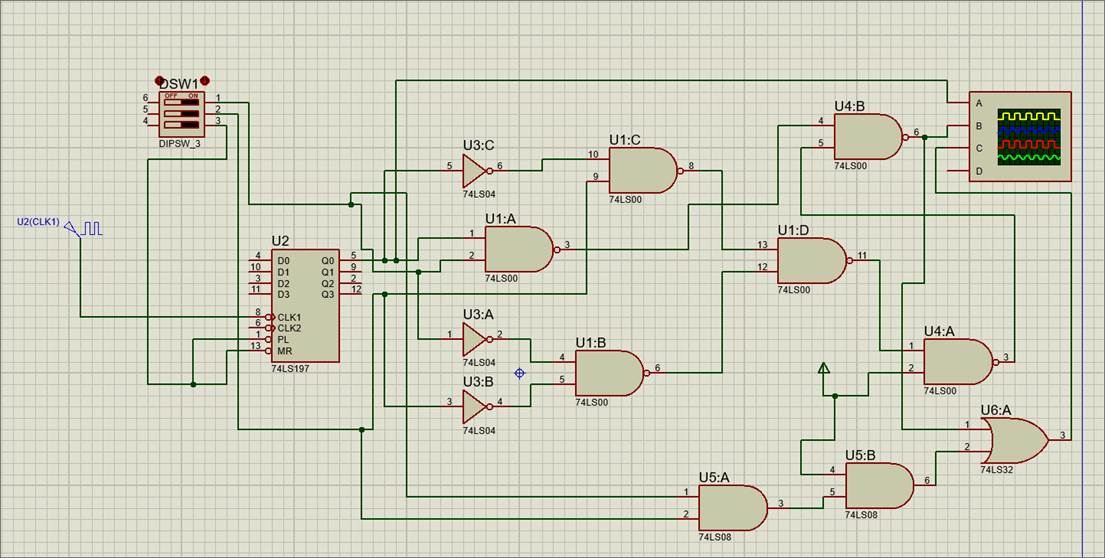

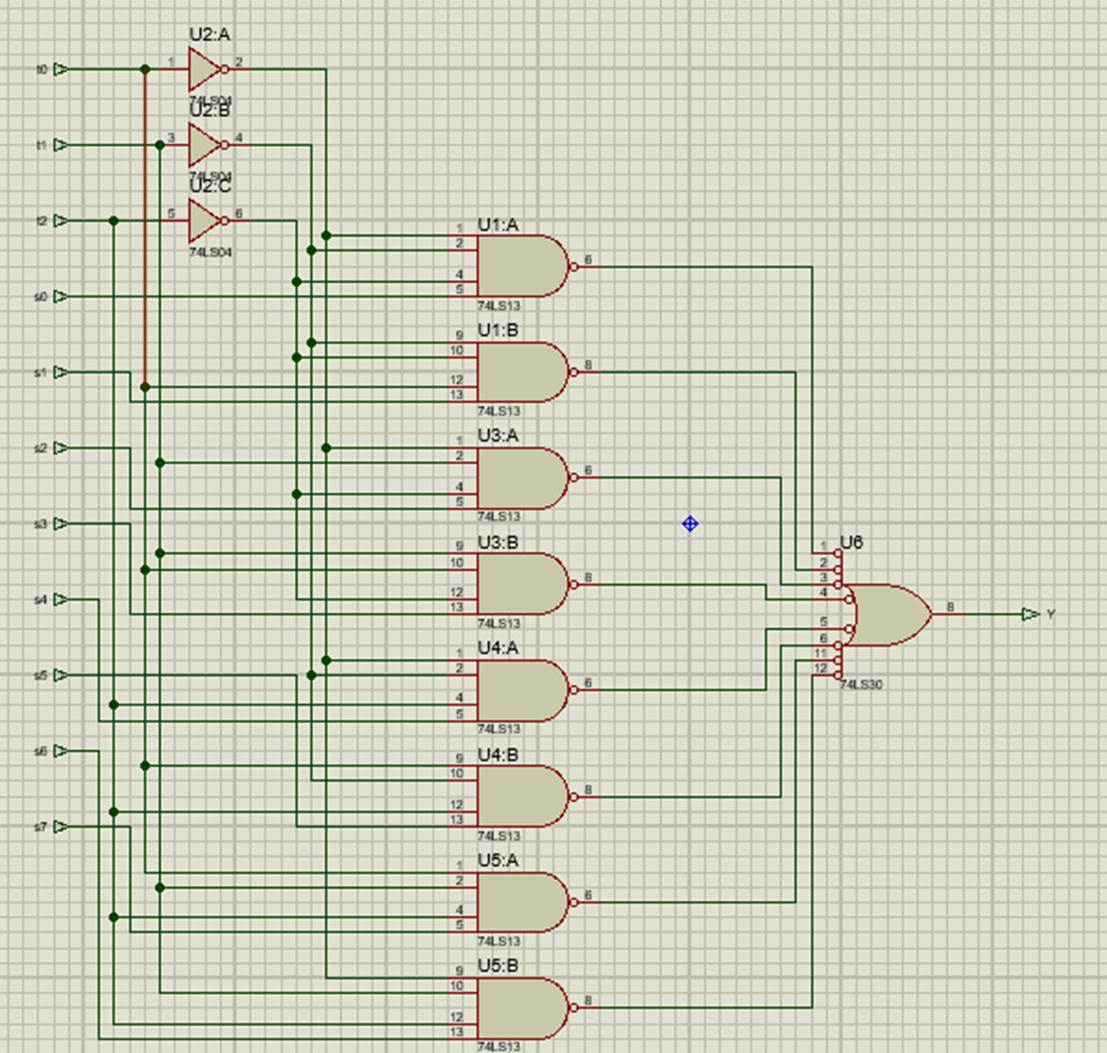

电路图:

实验图:

实验现象:在输出端得到稳定的输出前,出现了形状是宽度仅为时差的窄脉冲。

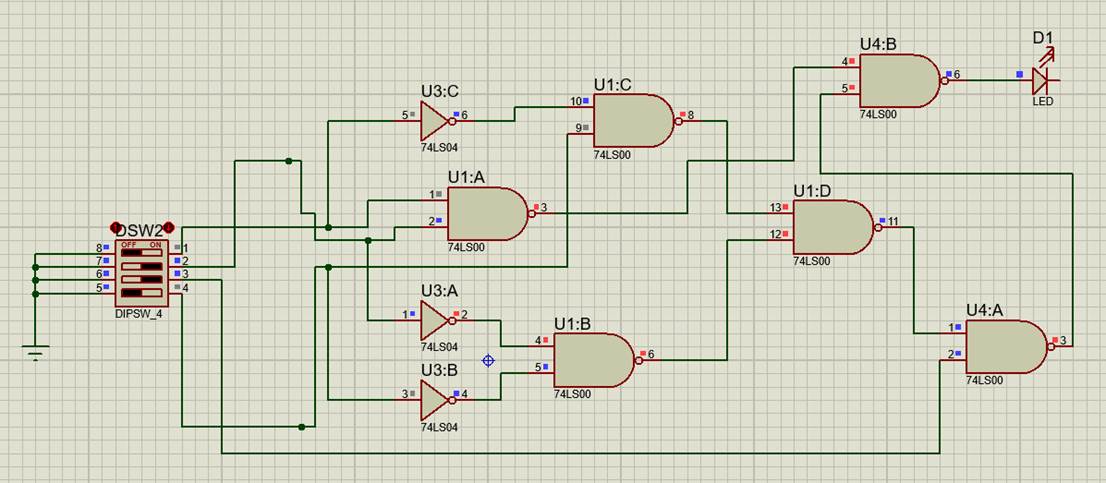

2.竞争冒险(静态测试)

(4)

用模拟开关s1、s2、s3、s4分别作为A、B、C、D变量的输入端,并只使用74ls00(与非门)实现函数F,将电路的输出F接入LED“0 1”显示器。

A=1;B=1;C=1;D=1;F=1;

A=0;B=0;C=0;D=0;F=1;

A=0;B=1;C=1;D=0;F=0;

真值表:

3.竞争冒险并消除(动态测试):

(4)

只采用与非门和非门连接电路,并接入10kHZ的脉冲,可以观察到毛刺现象。逻辑化简后, 。由于B、C、D接入的是高电位的模拟信号,A接入脉冲信号,在特定时刻,F会变成

。由于B、C、D接入的是高电位的模拟信号,A接入脉冲信号,在特定时刻,F会变成 ,这个时候由于门电路传输延迟,会产生竞争冒险。为了消除冒险,可采用添加冗余项的做法,使得

,这个时候由于门电路传输延迟,会产生竞争冒险。为了消除冒险,可采用添加冗余项的做法,使得 ,使得F不再被

,使得F不再被 的影响。

的影响。

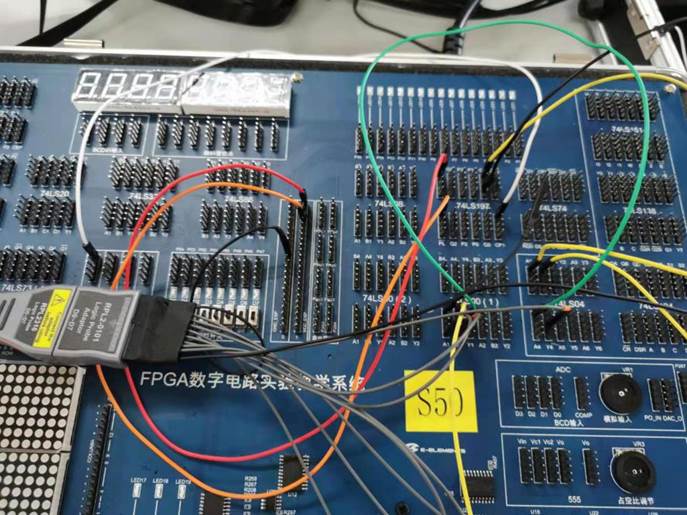

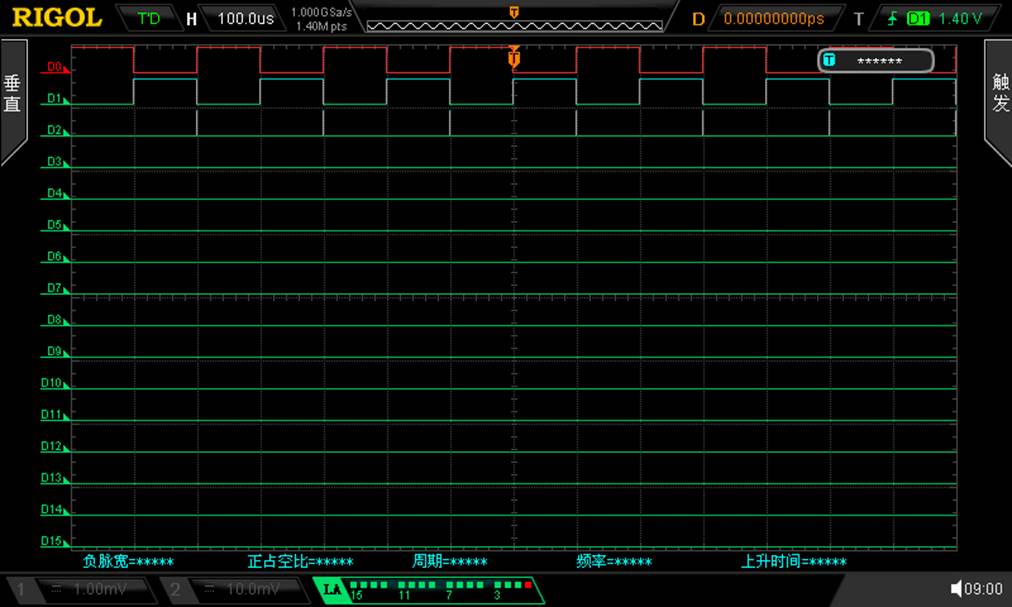

电路图:

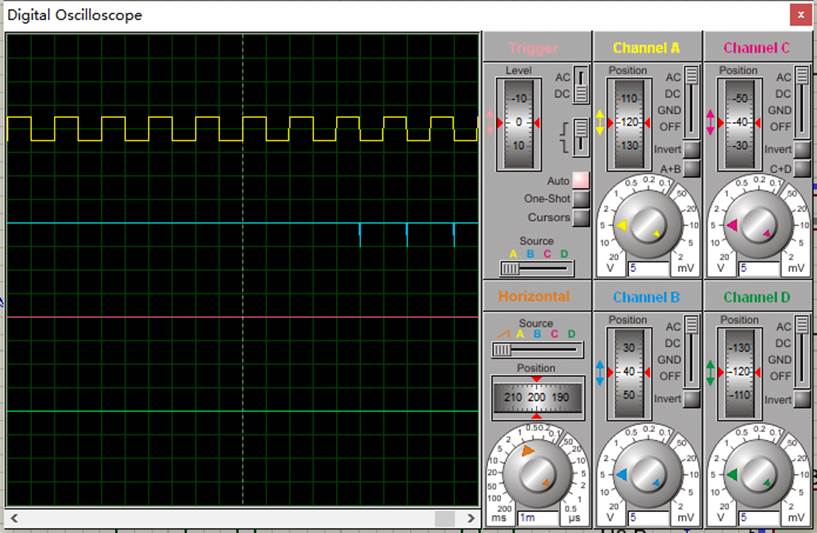

仿真图:

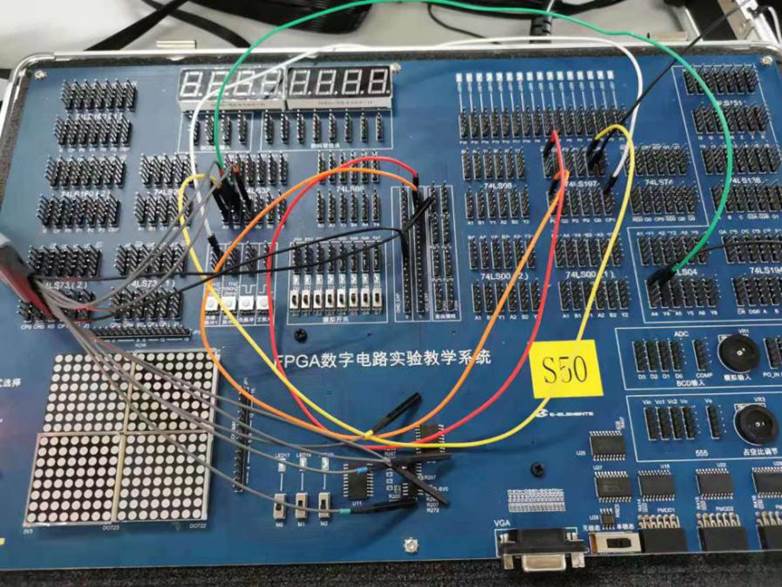

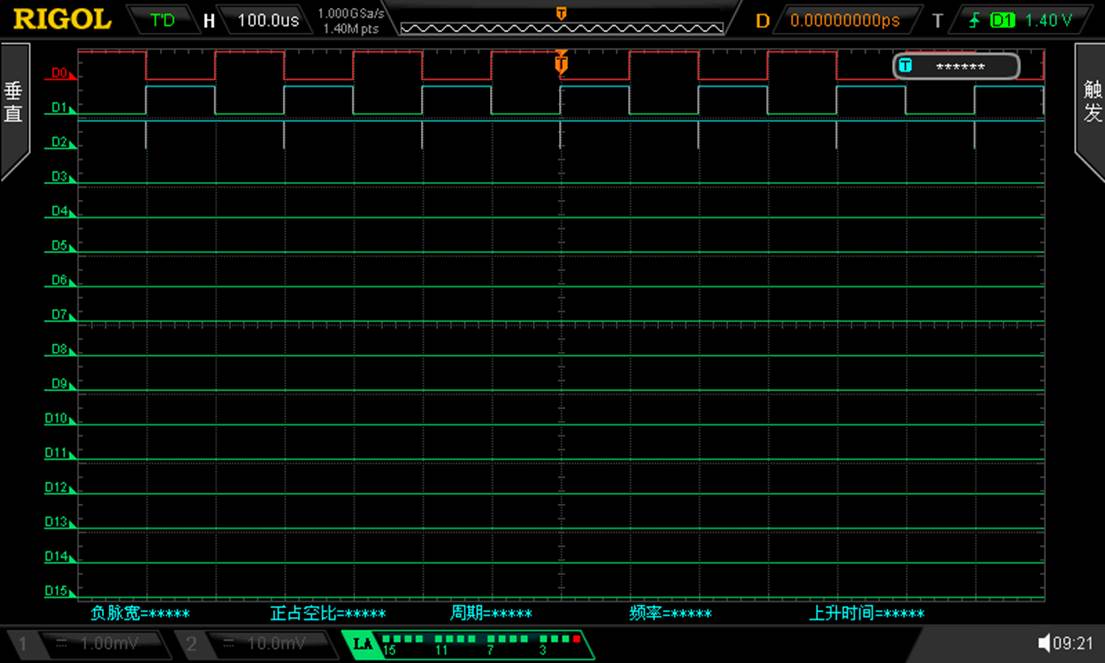

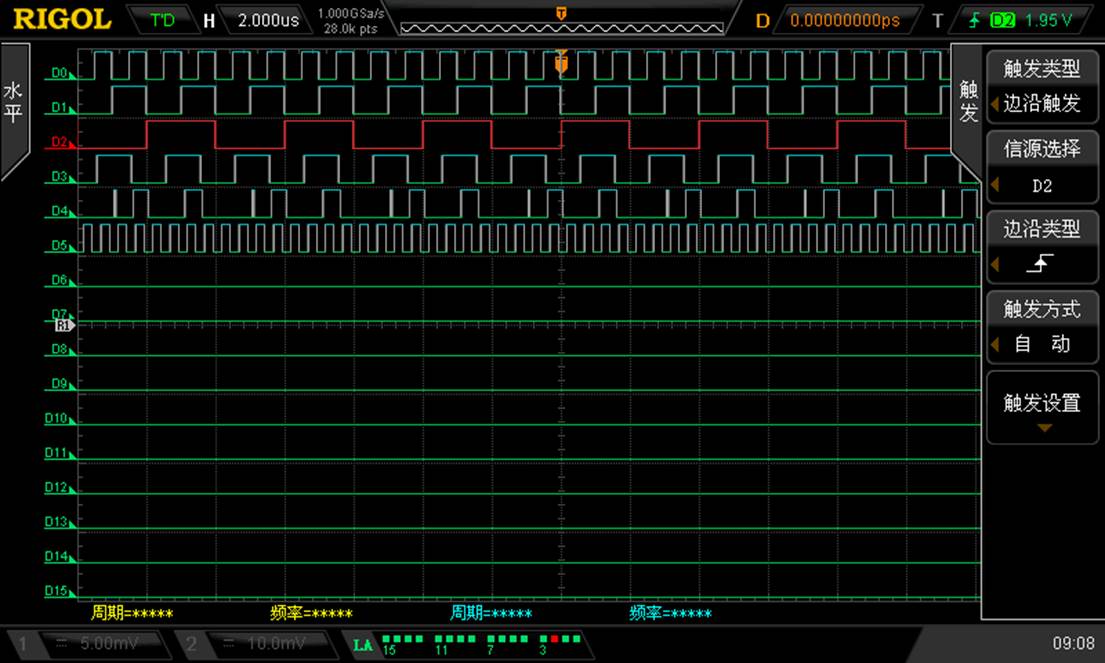

实验图:

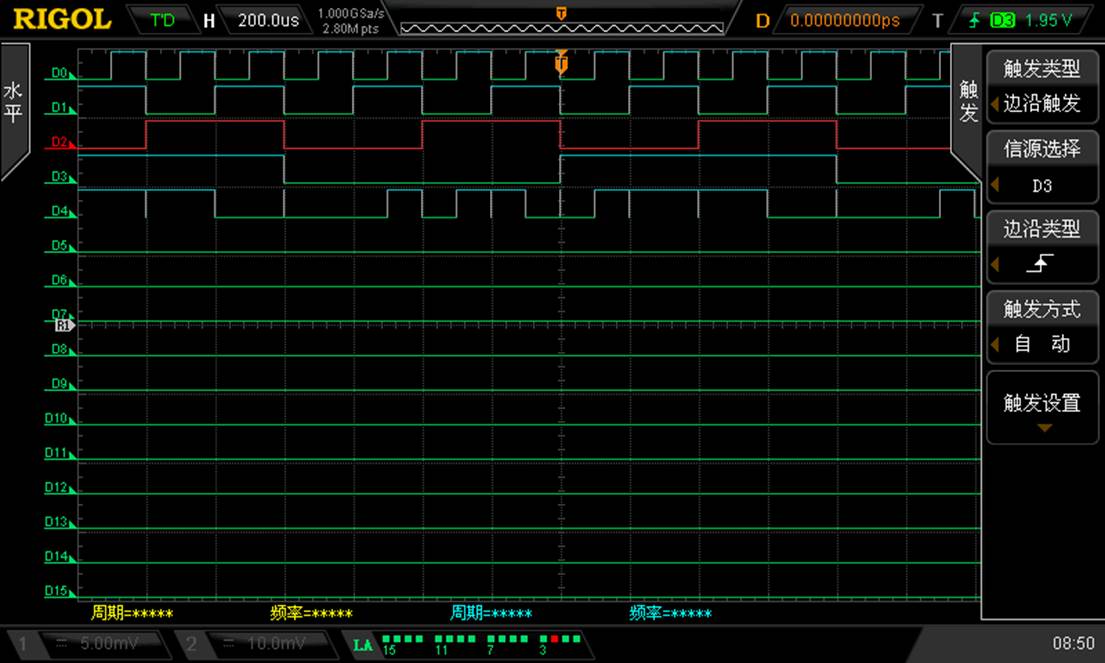

实验现象:D0为A的脉冲信号,D1为原电路产生的信号,可观察到毛刺现象,D1为添加冗余项的结果,可观察到毛刺现象消除。

实验三 格雷码与七段数码管

一、实验目的

1.学习格雷码和二进制码的相互转换;

2.学习七段数码管的控制方式。

二、实验要求

系统输入:逻辑电平、脉冲信号;

系统输出:LED、七段数码管;

系统功能:实现格雷码和二进制码相互转换;

七段数码管显示4位二进制数。

三、实验内容

1.0 总概括

1.0.1 五位二进制码转格雷码(静态实验)

1.0.2 五位格雷码转二进制码(静态实验)

1.0.3 四位格雷码转二进制码(动态实验)

1.0.4 四位二进制码转格雷码(动态实验)

1.0.5 四位二进制码转十六进制并显示在七段数码管(动态实验)

1.1 二进制码转格雷码

仿真图:

1.2 格雷码转二进制码

LED灯的击穿电压默认值是2.2V,在5V的逻辑电平经过异或门后,在二极管的作用下,电压下降至2.5V。经过多次异或门作用后,电压会下降至0.1V以下。因此LED的击穿电压可以调整至0.01V,这样可以观察到正确的实验现象。

仿真图

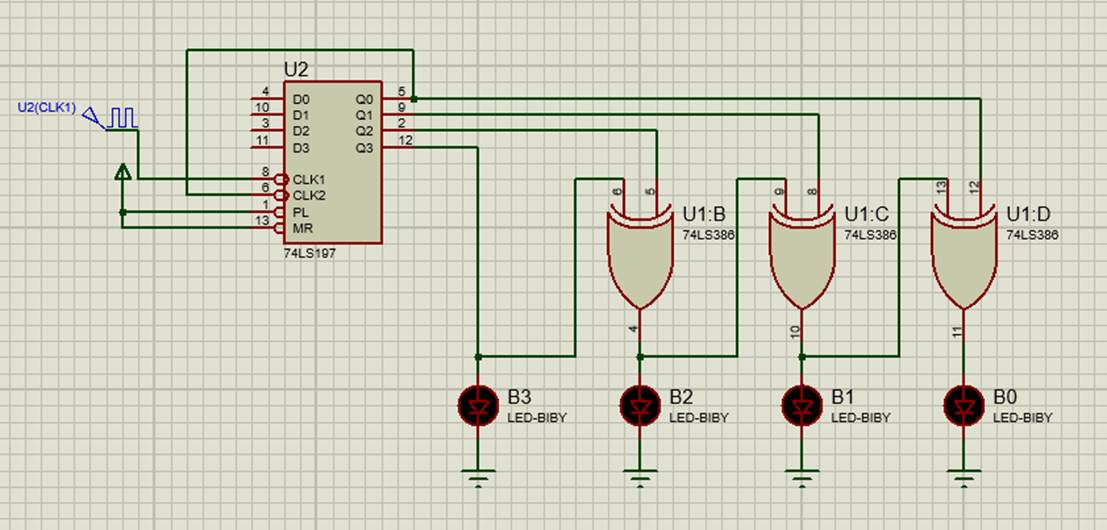

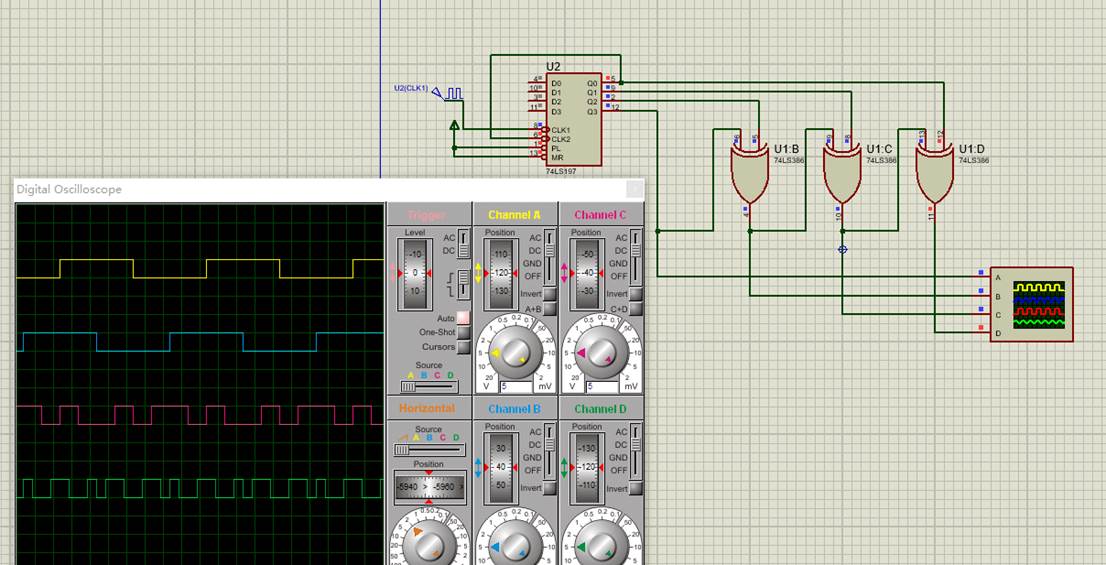

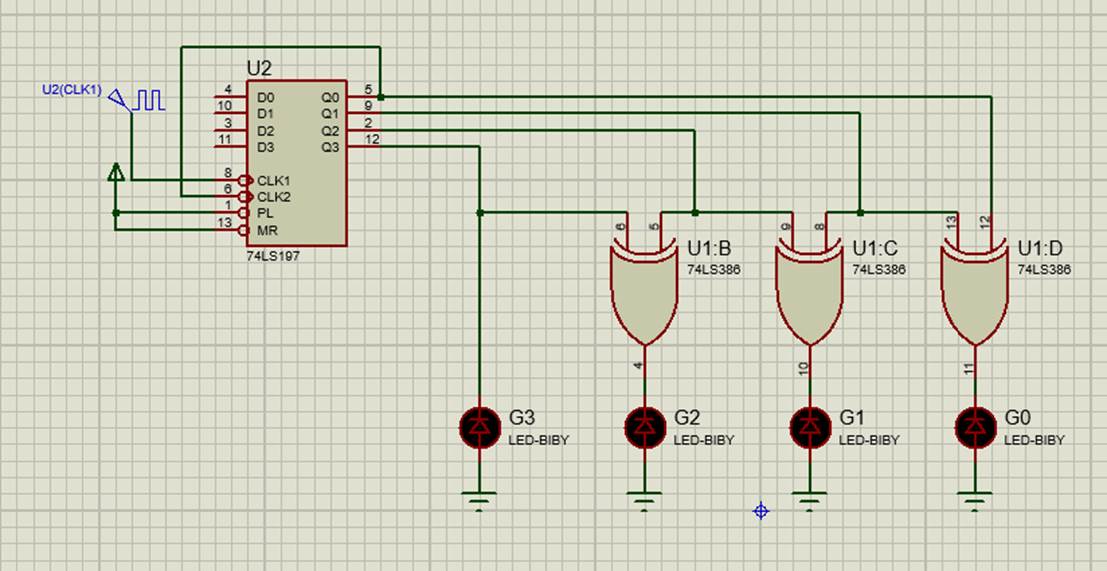

1.3 四位格雷码转二进制码(动态实验)

转换方式与五位格雷码转二进制码相同,这里才用74LS197作为输入端,观察LED的动态变换。

1.4 四位二进制码转格雷码(动态实验)

转换方式与五位二进制码转格雷码相同,这里才用74LS197作为输入端,观察LED的动态变换。

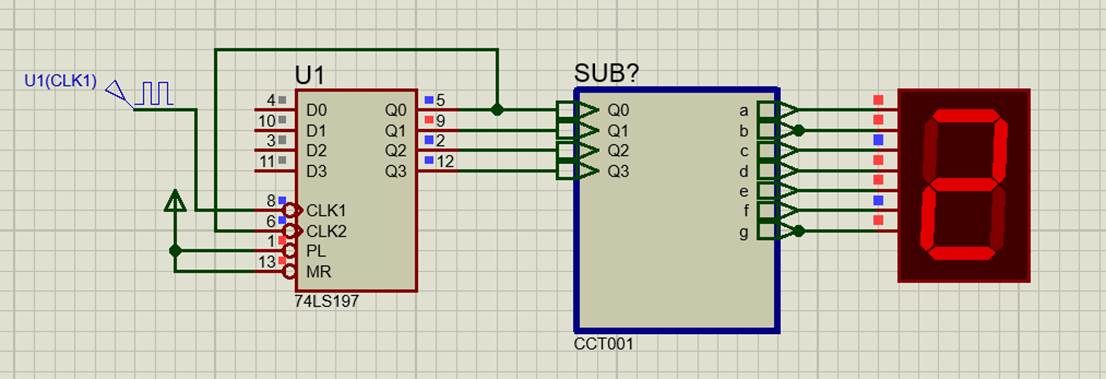

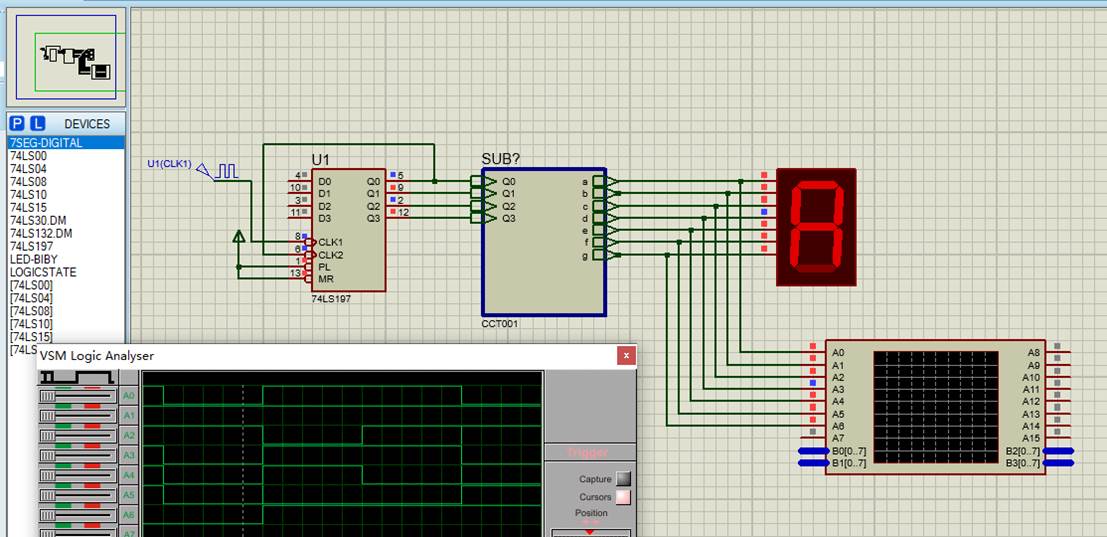

1.5 四位二进制转十六进制输出至七段数码管

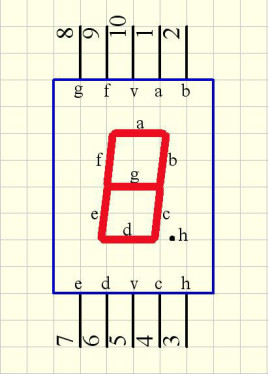

七段数码管的管号编号如下图:

转换的真值表情况如下表:

| Q3 | Q2 | Q1 | Q0 | a | b | c | d | e | f | g |

|---|---|---|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

| 0 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 1 |

| 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1 |

| 0 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 |

| 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 |

| 1 | 0 | 1 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 1 |

| 1 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 |

| 1 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 1 |

| 1 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 1 |

| 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 |

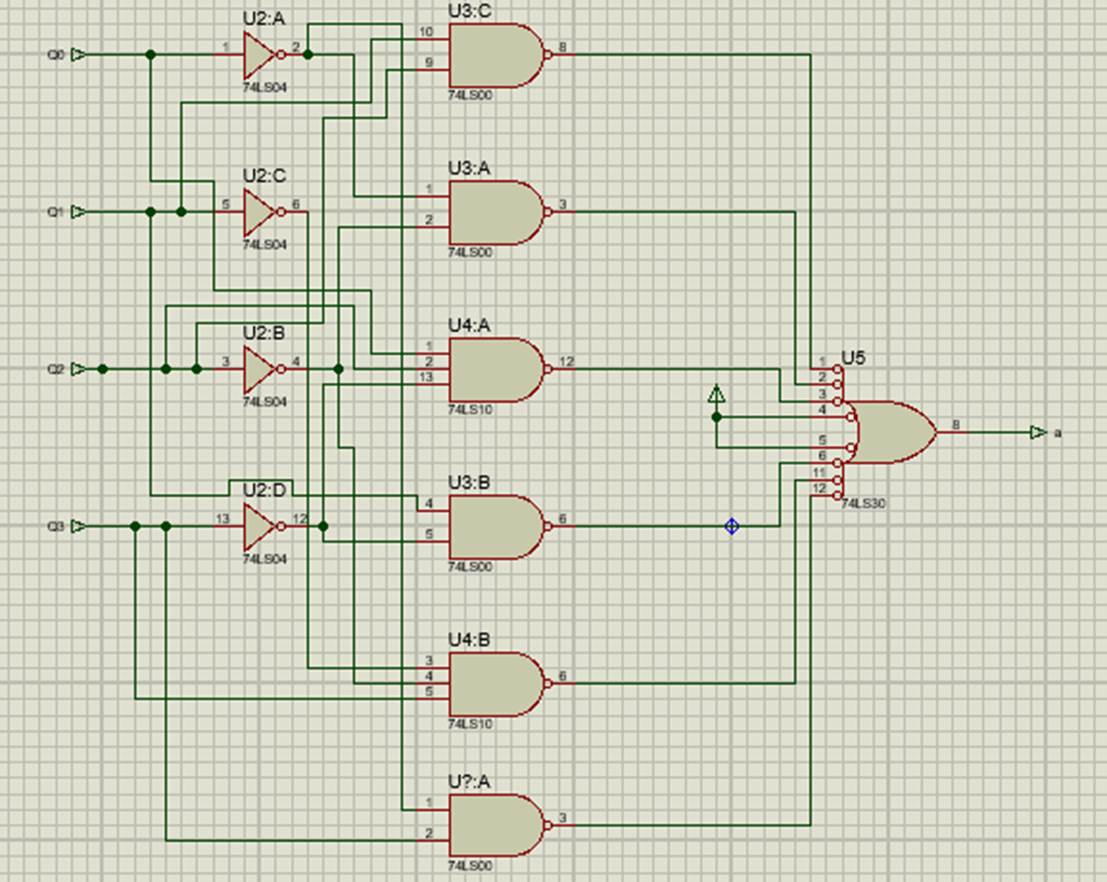

根据真值表,可得a-g每一条管受四位二进制码的控制情况,进行逻辑化简后得到如下表达式:

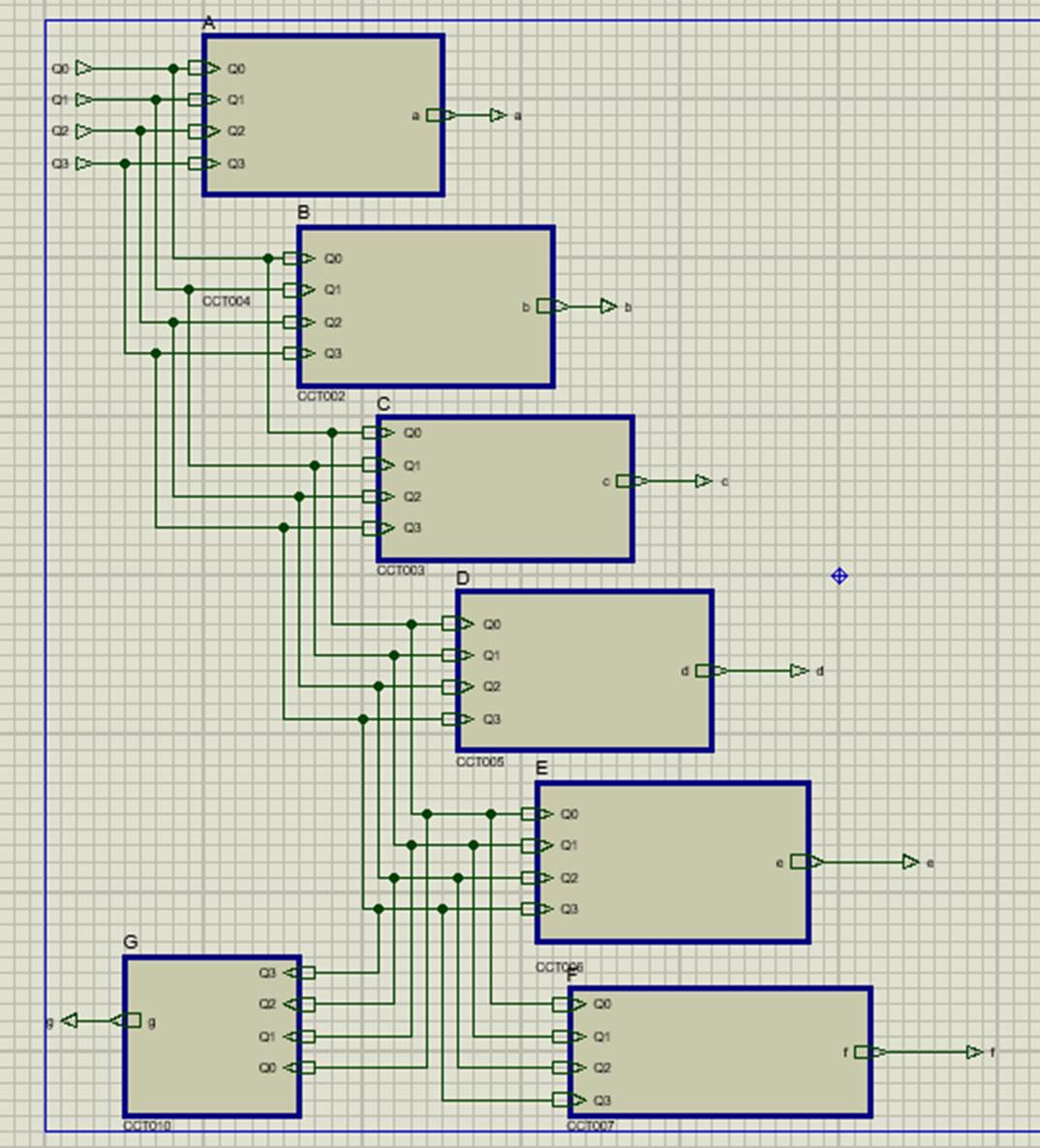

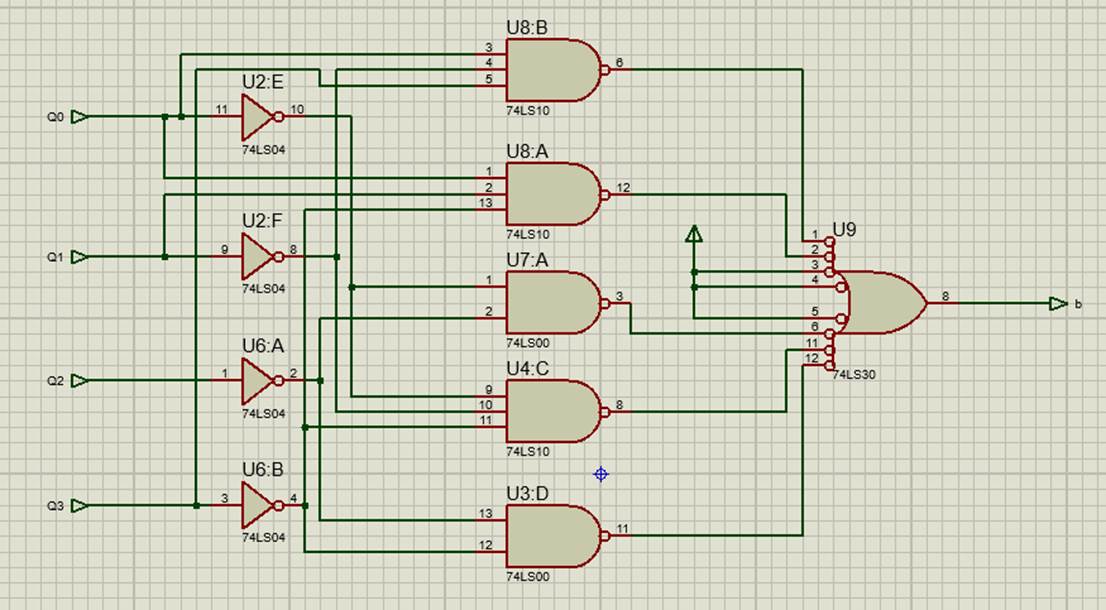

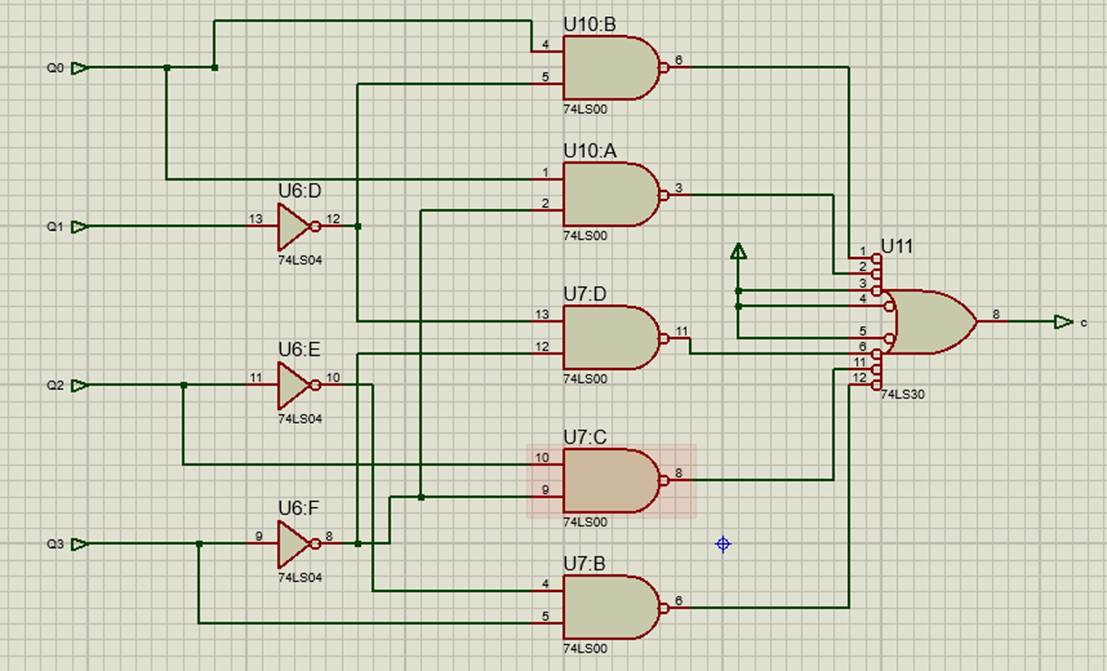

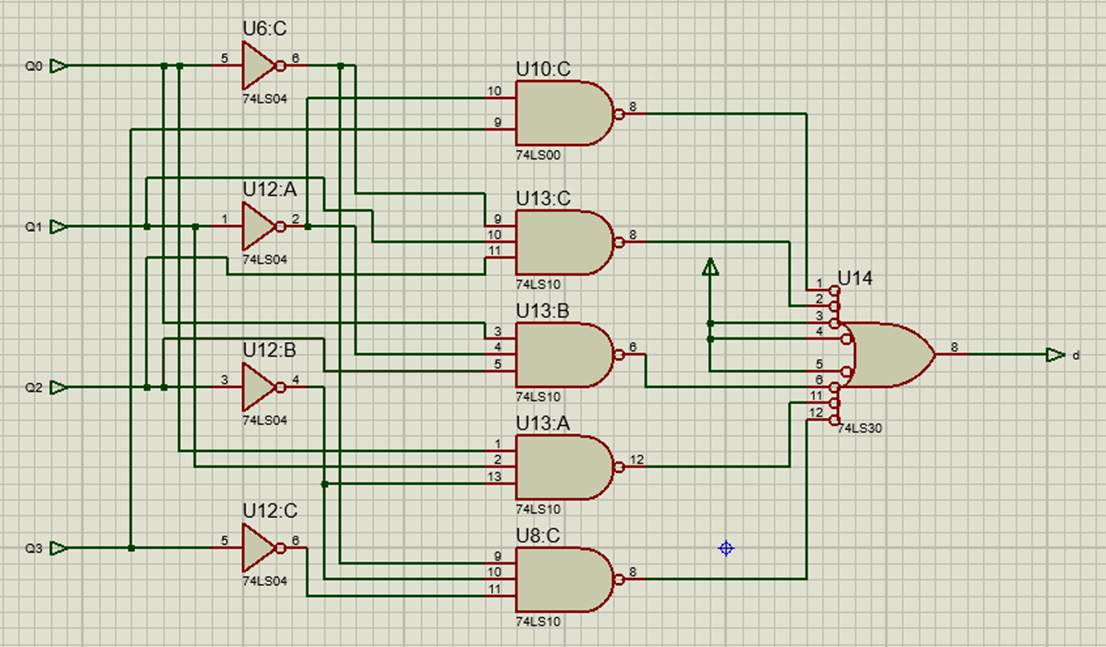

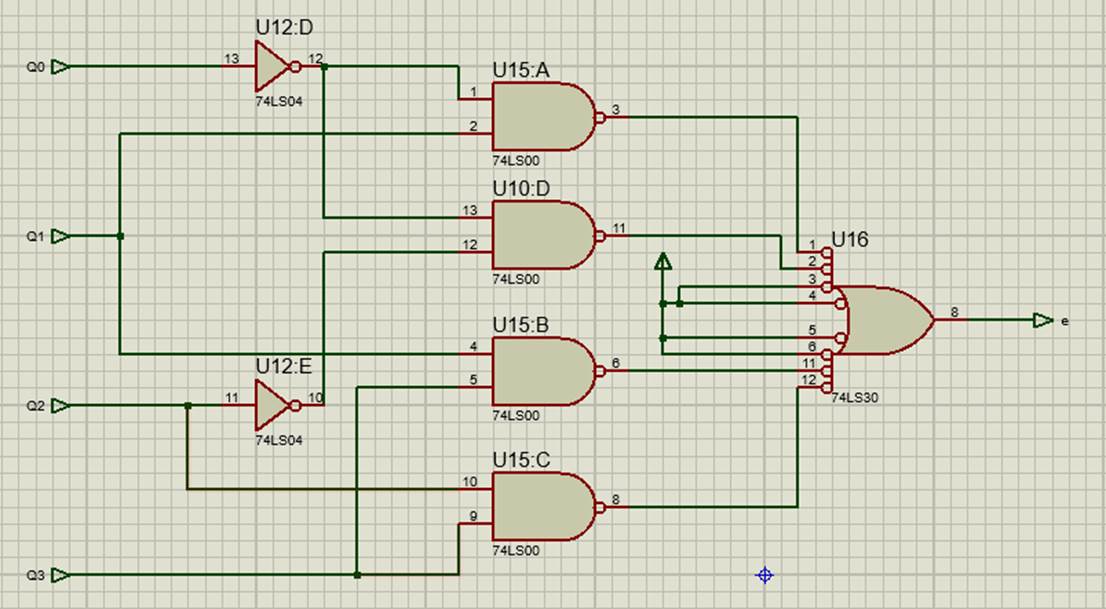

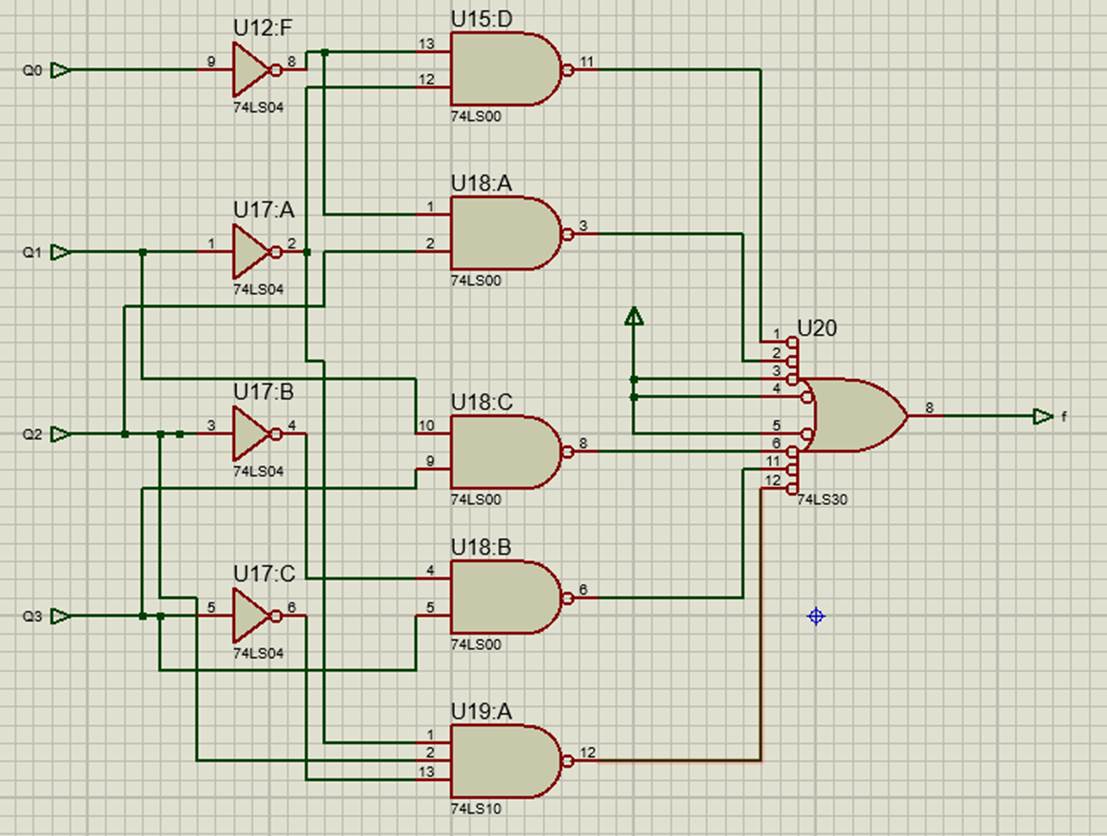

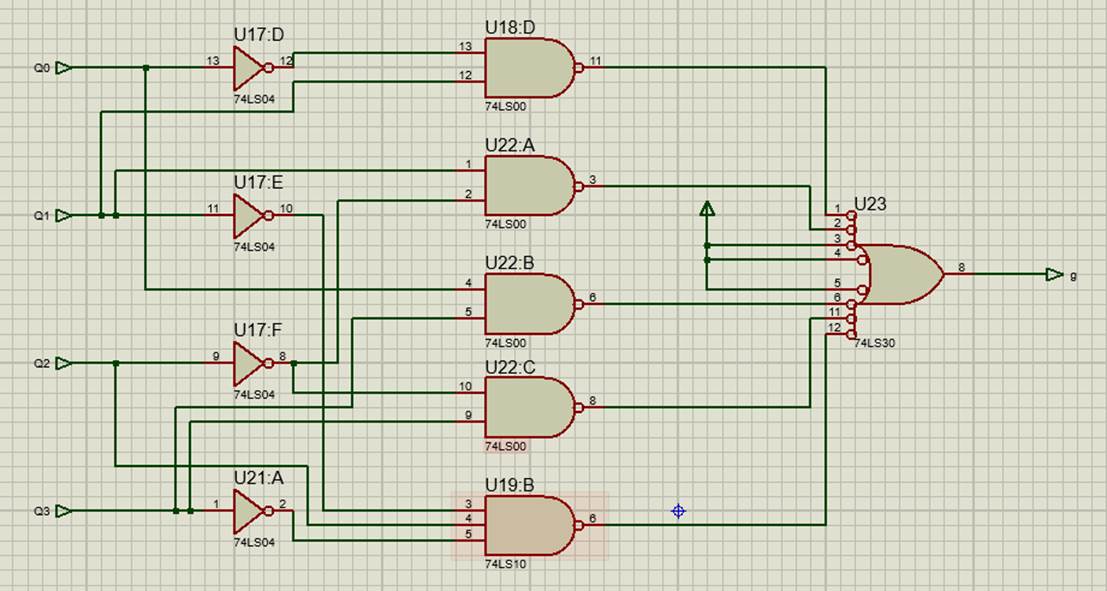

根据7条逻辑表达式,可画出电路图如下:

SUB?子电路图如下:

A子电路图如下:

B子电路图如下:

C子电路图如下:

D子电路图如下:

E子电路图如下:

F子电路图如下:

G子电路图如下:

实验结果:

实验四 七段数码管

一、实验目的

7段数码管显示学号。

二、实验要求

系统输入:脉冲信号;

系统输出:八位七段数码管;

系统功能:显示学号(19308030)。

三、实验思路

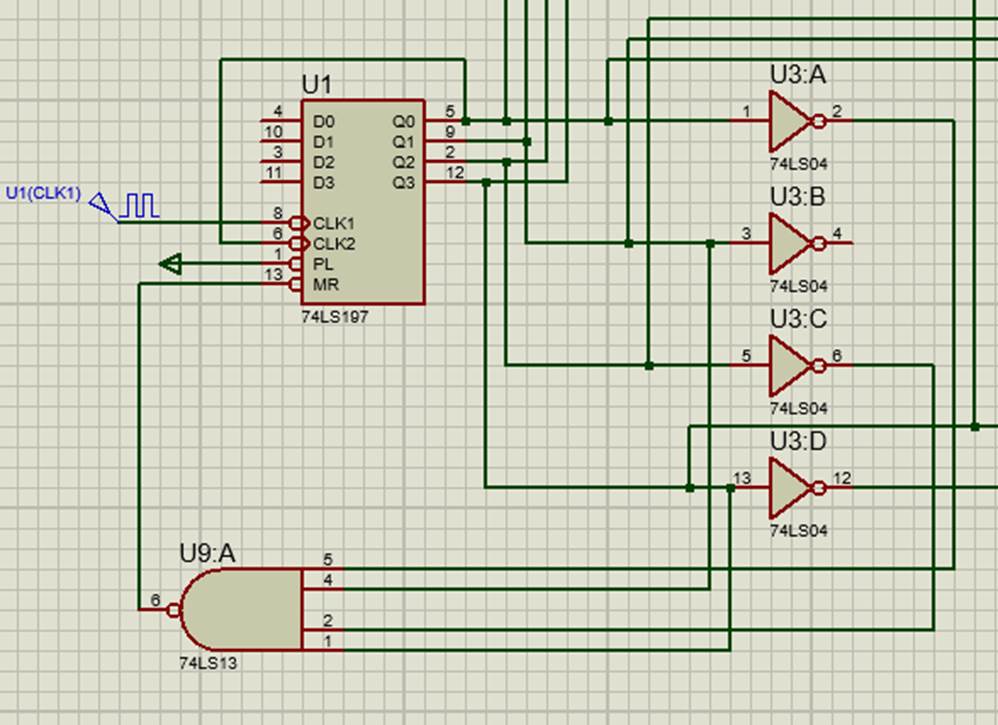

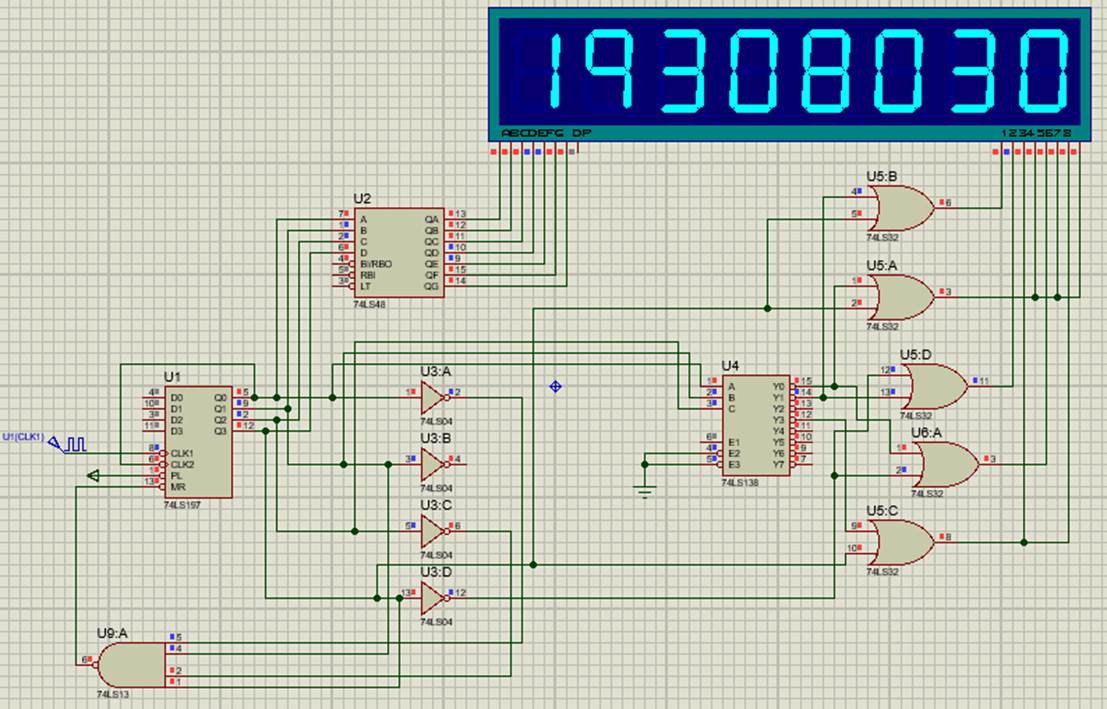

由于实验箱上八位七段数码管的受同一个BCD码引脚控制,无法同时显示八位数字不同的学号。在视觉上实现该操作,可以通过提高时钟频率,使得八位七段数码管的快速切换在肉眼上分别不出,产生视觉停留实现。

考虑第一种思路:

第一个时钟周期,在第一个七段数码管显示数字1;

第二个时钟周期,在第一个七段数码管显示数字9;

第三个时钟周期,在第一个七段数码管显示数字3;

第四个时钟周期,在第一个七段数码管显示数字0;

第五个时钟周期,在第一个七段数码管显示数字8;

第六个时钟周期,在第一个七段数码管显示数字0;

第七个时钟周期,在第一个七段数码管显示数字3;

第八个时钟周期,在第一个七段数码管显示数字0;

即当时钟信号输出0001的时候,数码管位选1输入低电平,其他七个位选输入高电平,BCD码输入0001。那么,数码管位选需要三个门电路,BCD码输入也需要三个门电路。综合下来八个七段数码管,所需的门电路数量非常庞大,几乎不可能在试验箱中实现。

考虑第二种思路:

第0个时钟周期,在数码管位选4、6、8中显示0;

第1个时钟周期,在数码管位选1中显示1;

第3个时钟周期,在数码管位选3、7中显示3;

第8个时钟周期,在数码管位选5中显示8;

第9个时钟周期,在数码管位选2中显示9;

那么,这种思路使得BCD码的输入与时钟信号输出相同,可直接相连,与前一种做法相比,差不多节省了一半的门电路。

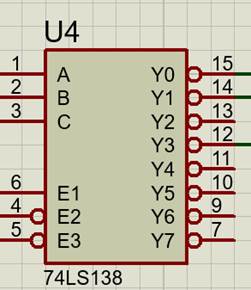

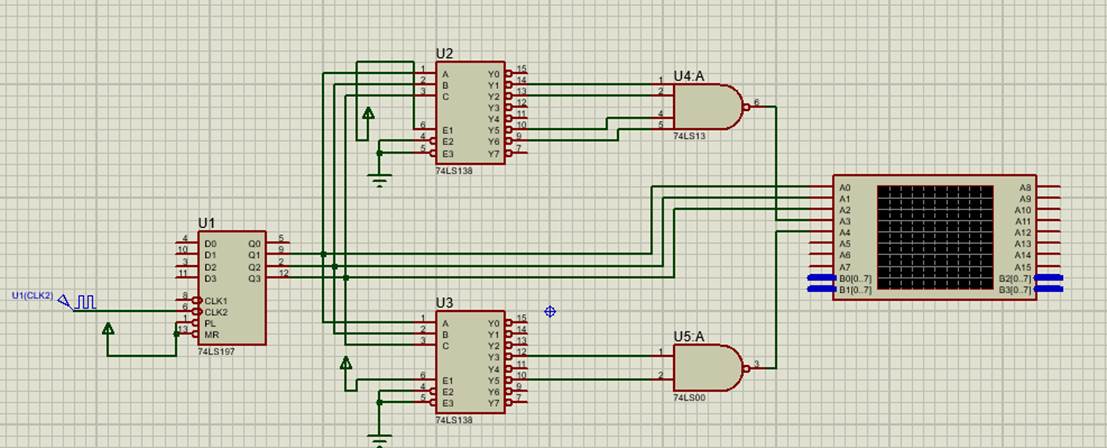

先考虑位选输入,引入一个元件——74LS138(38译码器)。

A、B、C端口输入二进制信号,在Y端口对应十进制数字的位置会输出低电平,其余端口输出高电平。由于七段数码管位选位置为低电平有效,使用该器件可以很方便地进行位选。

以上是学号中没有出现8和9的时候的情况。先考虑8和9如何相连:

首先,0-7的时候,74LS197中的Q3输出0,此时0-7对应的数字显示。则上述电路中76LS138中Y端口输出可以与Q3进行或运算,使得8-15的输出不影响0-7的输出。对于8,可以采用Q3取反再与Y0进行或运算,使得当时钟信号输出8的时候,可以产生一个低电平。对于9也是类似的。

那么,电路看似已经连成了,其实棋差一招。

时钟信号输出四位二进制,而10-15这一部分是电路中不需要的。那么当时钟信号计数到10的时候,我们需要将时钟信号归零。76LS197中MR端口提供了该功能。

当时钟计数到10的时候,Q端口输出1010,则此时需要将MR置为0。

那么综上,电路实现完成。

需要注意的是,在仿真的过程中,我们采用38编码器将时钟信号输出编码成七段数码管abcdefg管位控制的信号,而实验箱上,该引脚已经被封装成为BCD码,不需要该操作。

四、实验结果

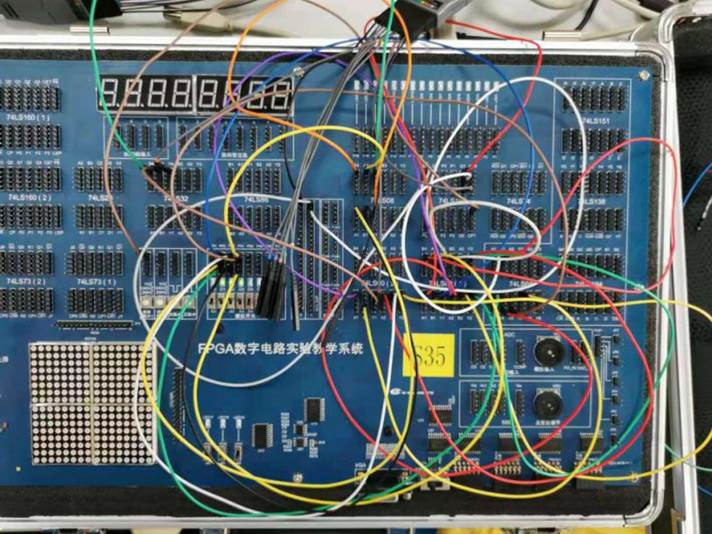

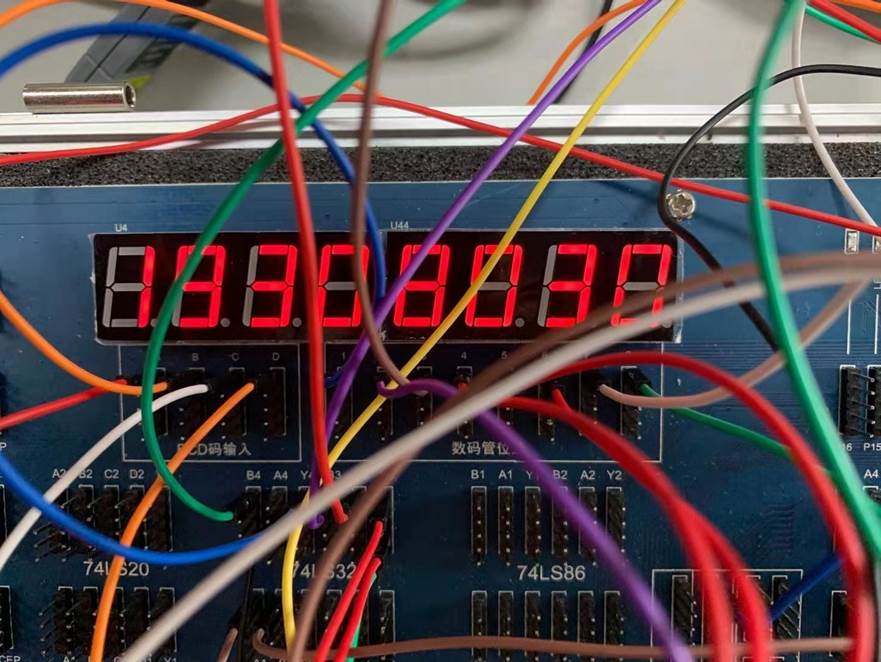

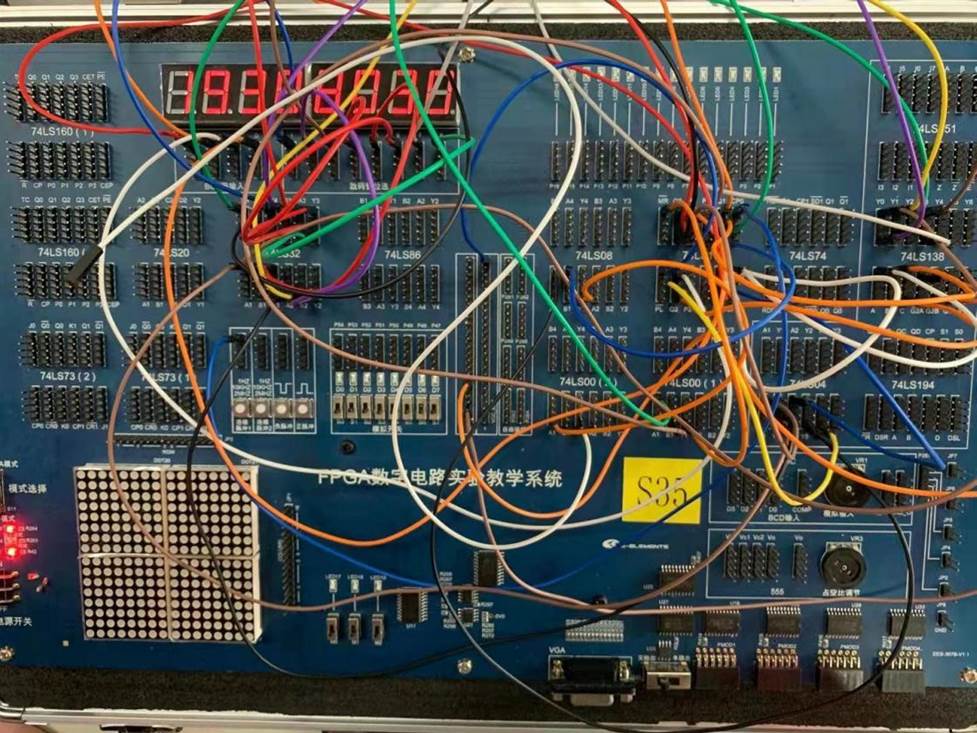

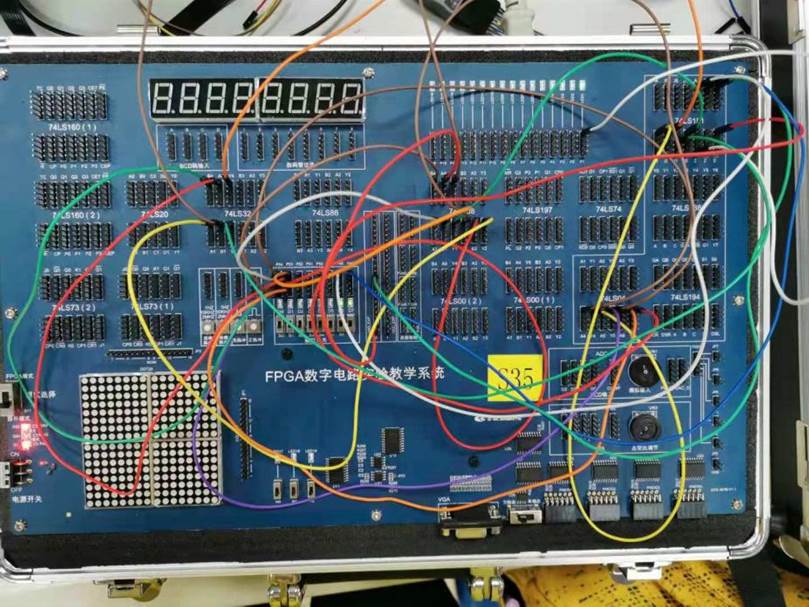

4.1 试验箱结果

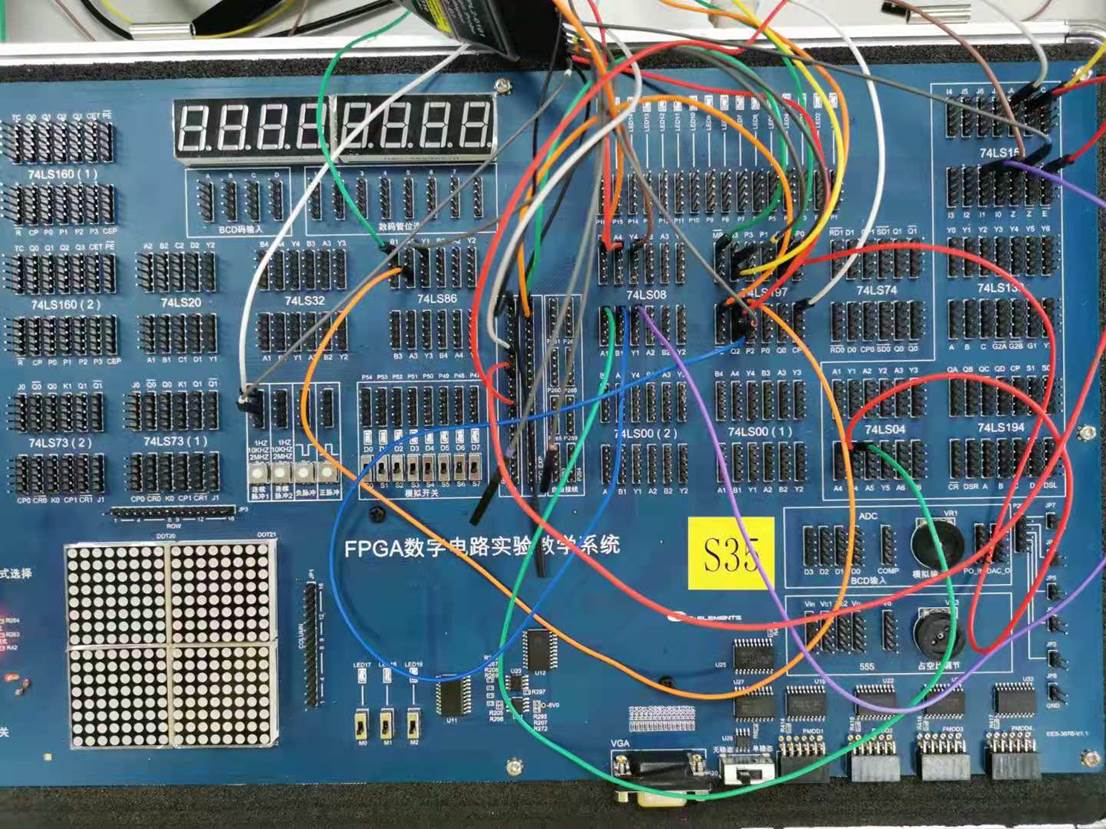

4.2 试验箱电路图

4.3 仿真结果及电路图

实验五 半加器与4-16译码器

一、带控制端的半加半减器

1.1 实验目的

了解半加器与半减器的原理,通过画出真值表后用卡诺图化简得到实现方法。

1.2 实验要求

系统输入:脉冲信号、逻辑电平;

系统输出:LED、示波器;

系统功能:

输入为S、A、B,其中S为功能选择口。当S=0时,输出Y为A+B及进位Cn;当S=1时,输出Y为A-B及借位Cn。

| S | 输入1 | 输入2 | 输出Y | 进/借位Cn |

|---|---|---|---|---|

| 0 | A | B | A+B | 进位 |

| 1 | A | B | A-B | 借位 |

1.3 实验思路

1.3.1 画出器件的真值表

| S | A | B | Y | Cn |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 | 0 |

1.3.2 根据真值表,列出表达式

1.3.3 根据表达式,进行逻辑化简

1.4 实验结果

1.4.1 试验箱结果

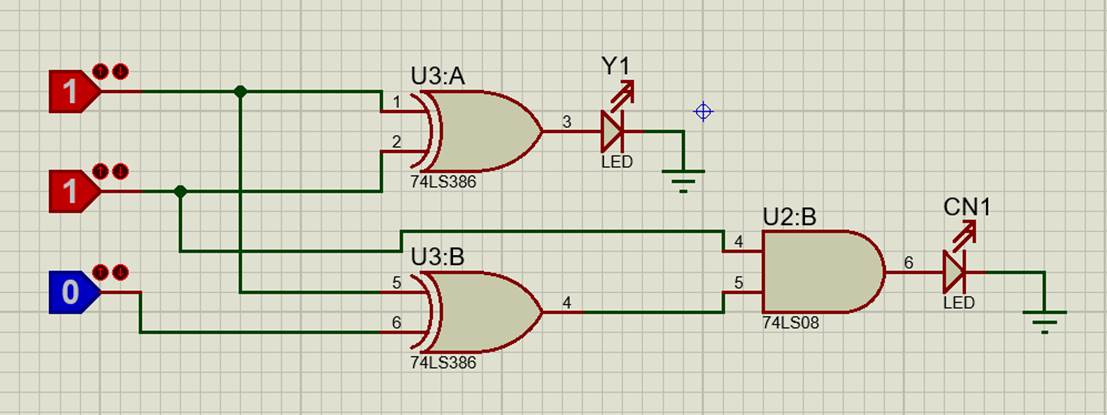

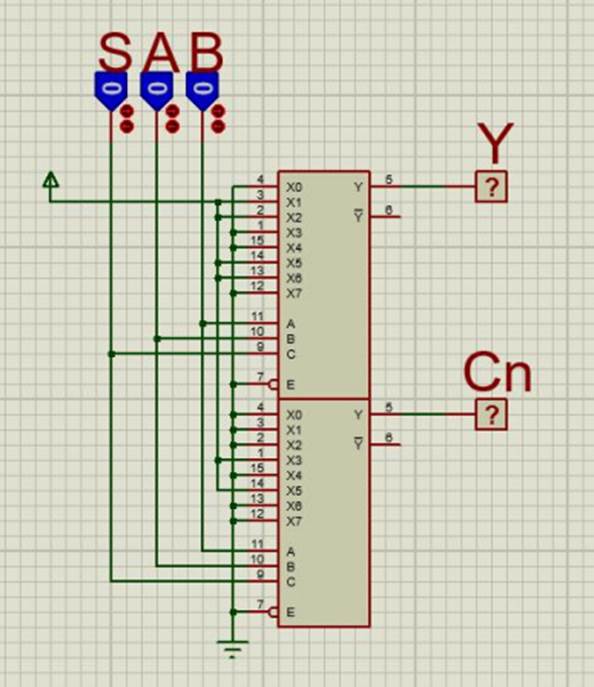

1.4.2 proteus静态实验结果

注:用逻辑门实现

注:用74LS138实现

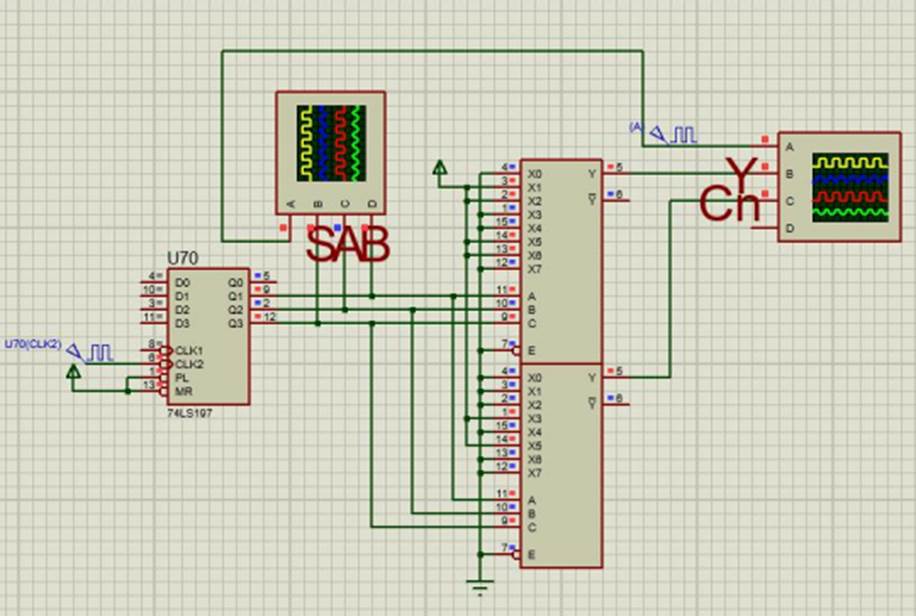

1.4.3 proteus动态实验结果

注:用逻辑门实现

注:用74LS138实现

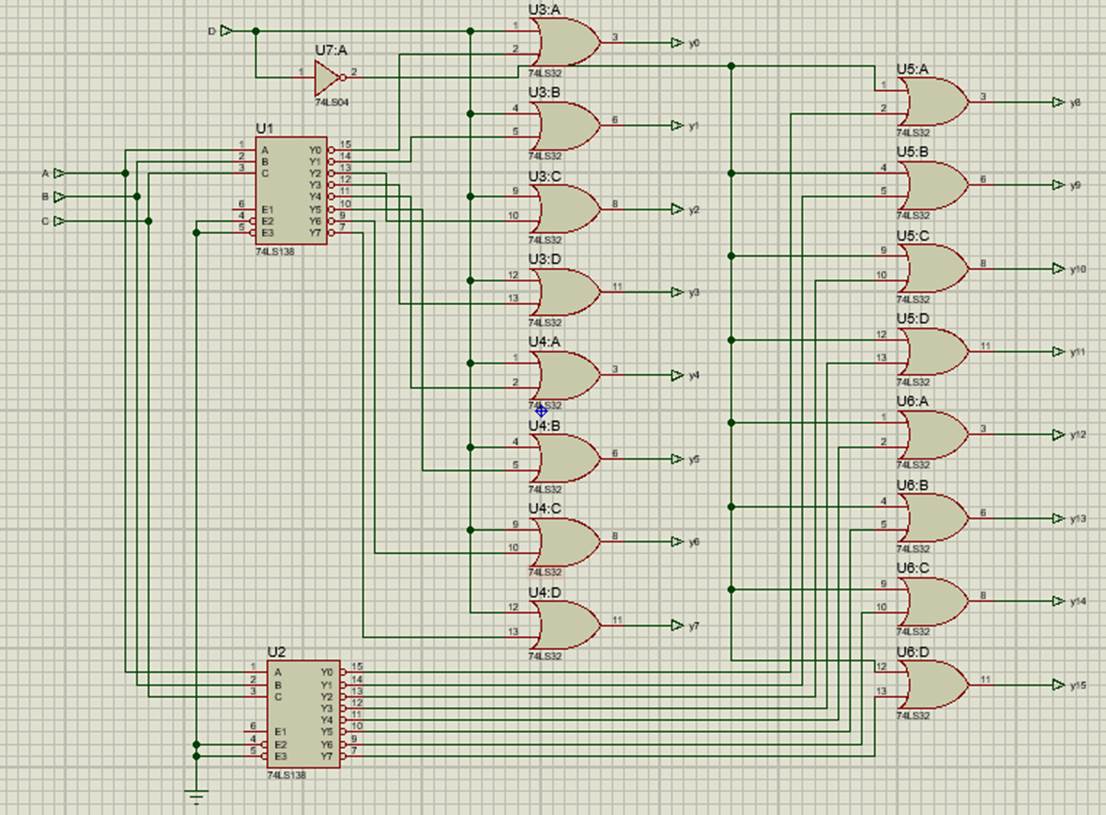

二、4-16线普通译码器

2.1 实验目的

了解4-16线译码器的实现原理,了解3-8译码器的使用方式。

2.2 实验要求

系统输入:脉冲信号、逻辑电平;

系统输出:LED、示波器;

系统功能:

使用74LS138实现一个4-16线普通译码器的设计(设计可不考虑4-16线译码器的使能端 、

、 和G1),并通过静态测试和动态测试,在仿真环境下验证动态电路功能的正确性。

和G1),并通过静态测试和动态测试,在仿真环境下验证动态电路功能的正确性。

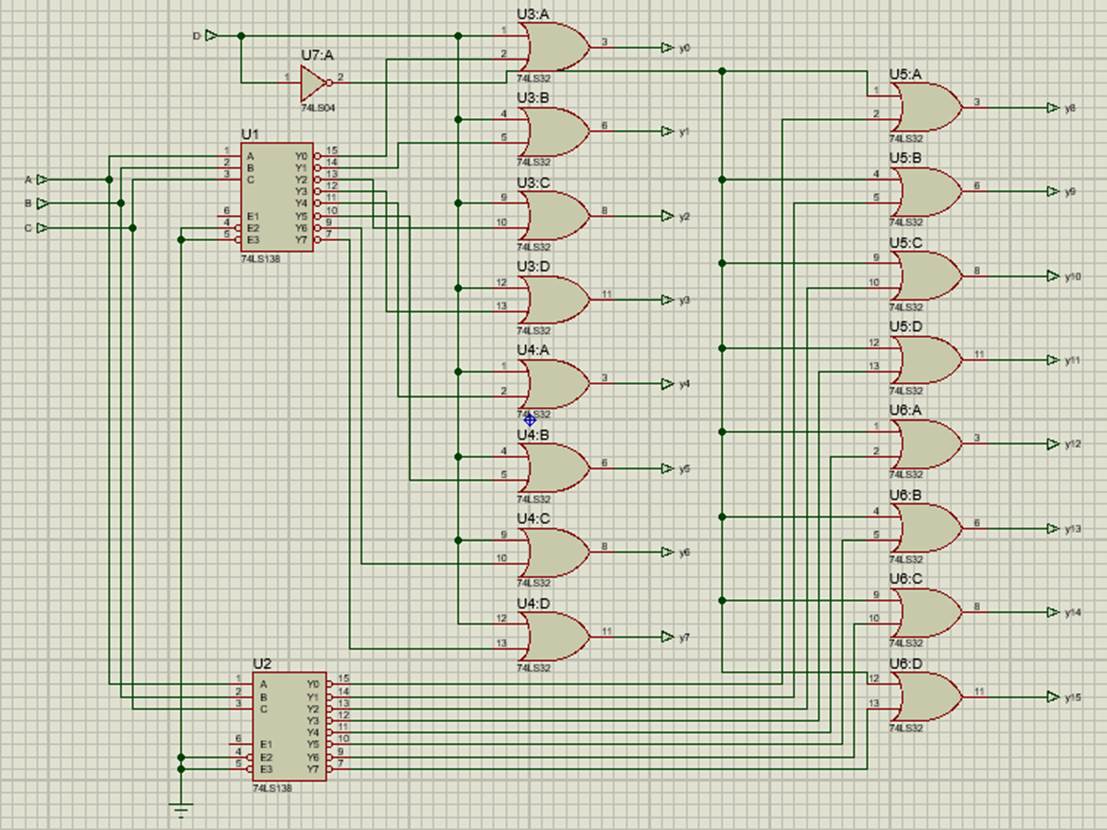

2.3 实验思路

采用两个74LS138,其中第一个控制0-7位的输出(不妨称之为A1),另一个控制8-15位的输出(不妨称之为A2)。则输入端s0、s1、s2作为A1的输入端,八位输出与s3做或运算;输入端s0、s1、s2作为A2的输入端,八位输出与 做或运算。

做或运算。

2.4 实验结果

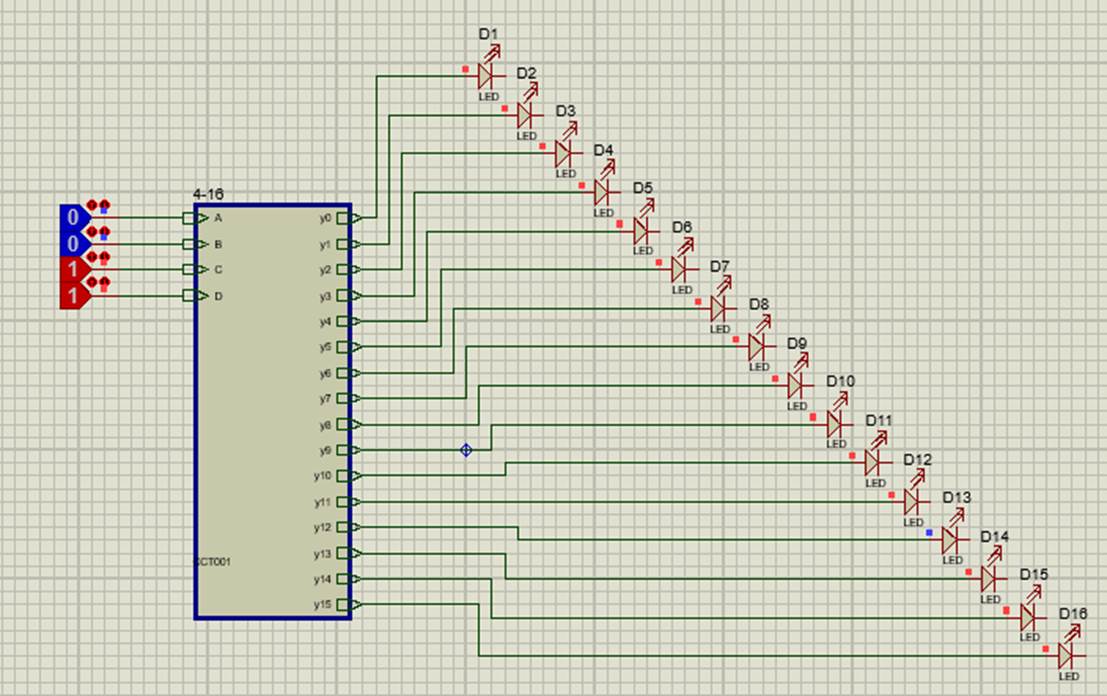

2.4.1 静态实验结果

注:图中A\B\C\D分别为s0\s1\s2\s3

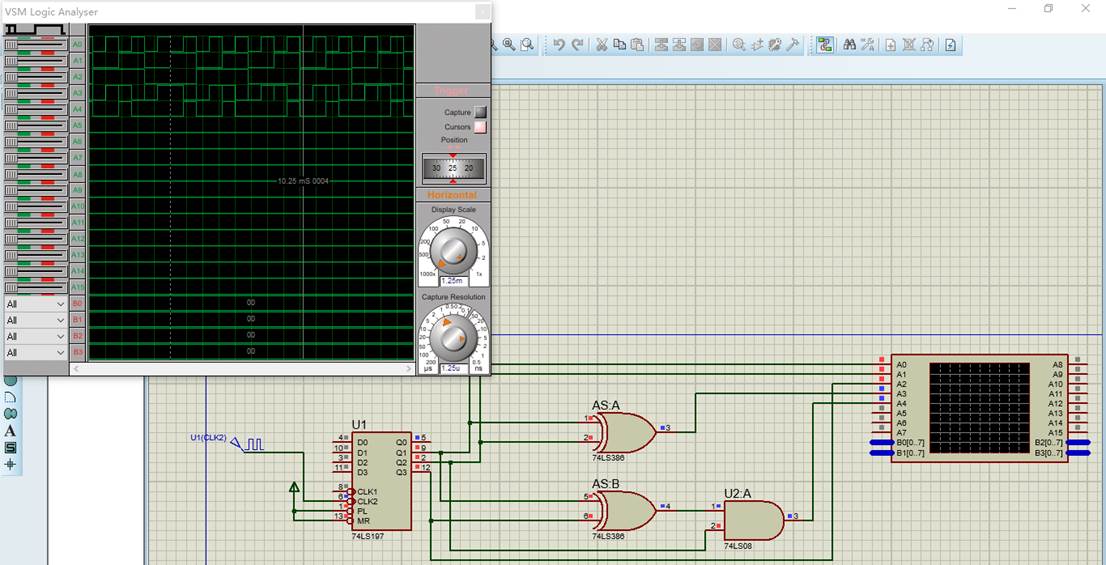

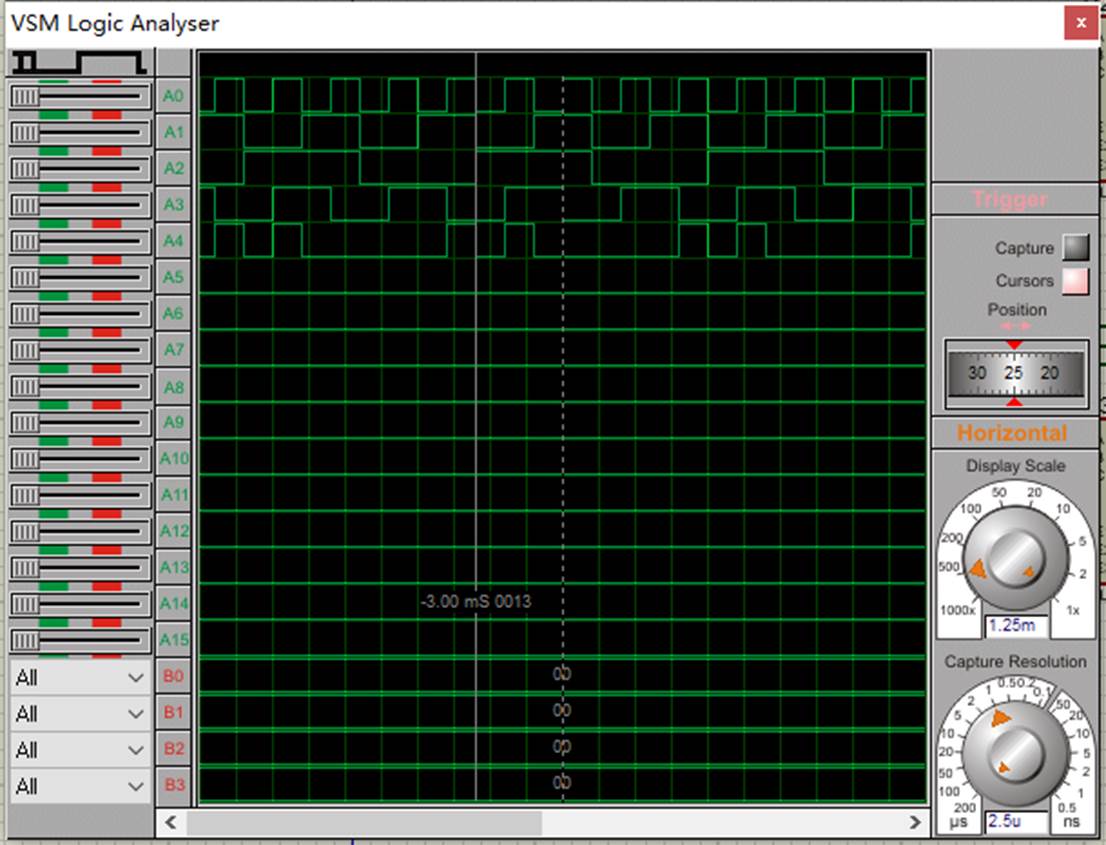

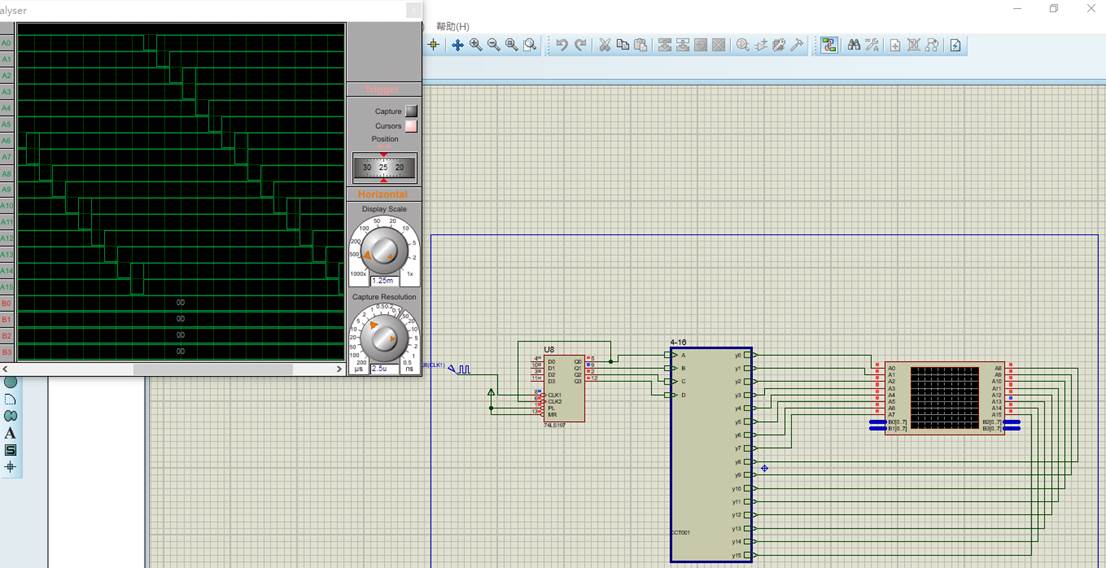

2.4.2 动态实验结果

注:图中A\B\C\D分别为s0\s1\s2\s3

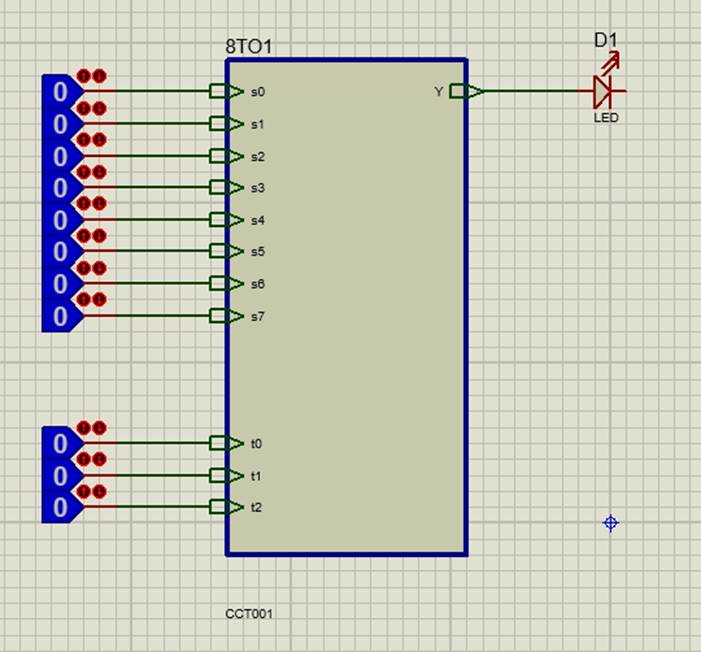

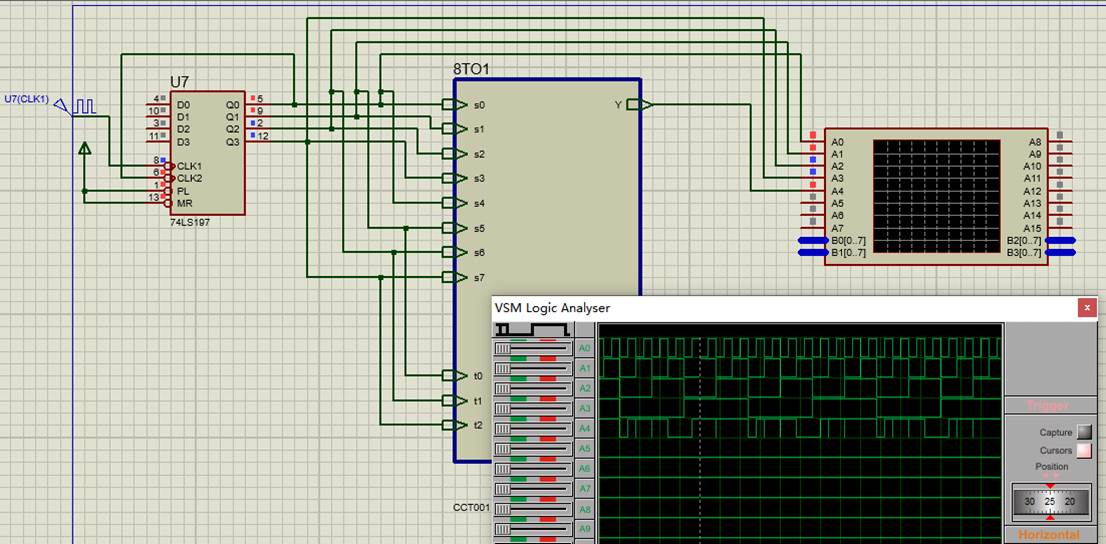

实验六 八选一选择器、算术单元与逻辑单元

一、八选一数据选择器

1.1 实验目的

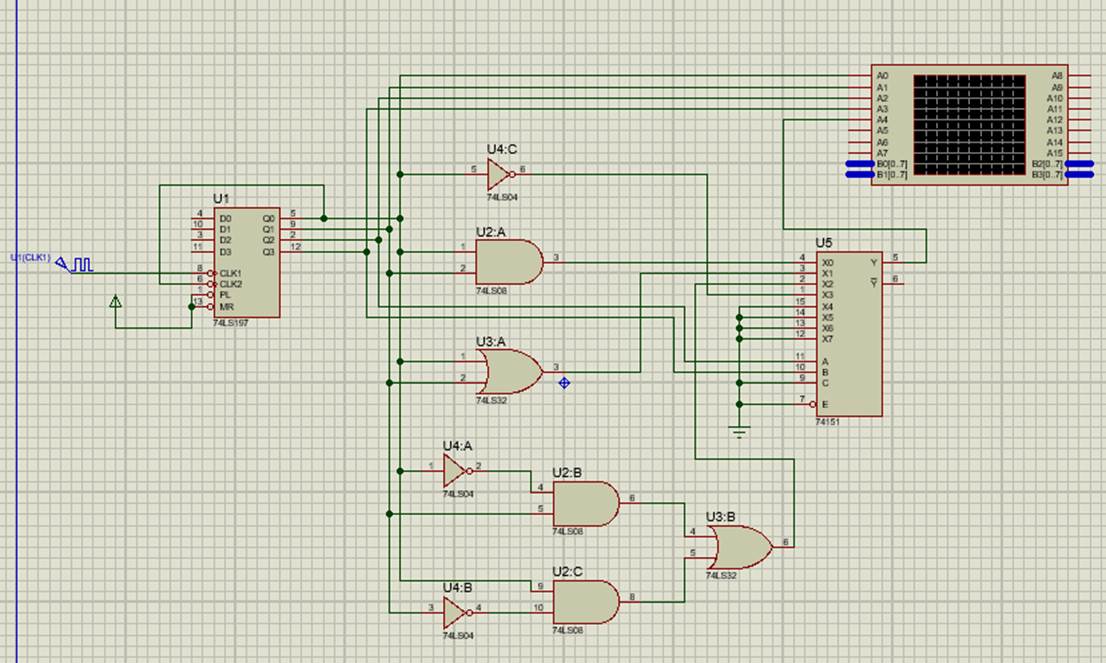

在Proteus环境下,使用门电路搭建一个八选一数据选择器,功能通74LS151,并通过静态测试和动态测试,在仿真环境下验证电路功能的正确性。

1.2 实验要求

系统输入:逻辑电平(静态实验)、74LS197(动态实验);

系统输出:LED;

系统功能:八选一数据选择器。

1.3 实验思路

设八位数据输入为s0\s1\s2\s3\s4\s5\s6\s7,信号选择为t0\t1\t2,输出端为Y。

当t=000,则Y=s0;

当t=001,则Y=s1;

当t=010,则Y=s2;

当t=011,则Y=s3;

当t=100,则Y=s4;

当t=101,则Y=s5;

当t=110,则Y=s6;

当t=111,则Y=s7;

因此,得到输出端的表达式:

1.4 实验结果

1.4.1 静态实验

1.4.2 动态实验

1.4.3 子图

注:子图

二、算术单元设计

2.1 实验目的

在Proteus上,使用74HC151实现AU(Arithmetic Unit,算术单元)设计。设计一个带控制端的半加半减器,输入为S、A、B,其中S为功能选择口。当S=0时,输出Y为A+B及进位Cn;当S=1时,输出Y为A-B及借位Cn。

带控制端的半加半减器功能表

| S | 输入1 | 输入2 | 输出Y | 进/借位Cn |

|---|---|---|---|---|

| 0 | A | B | A+B | 进位 |

| 1 | A | B | A-B | 借位 |

2.2 实验思路

| S | A | B | Y | Cn |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 | 0 |

S为控制端,Y为输出结果

当S=0,代表A+B=Y,Cn代表进位标志位

当S=1,代表A-B=Y,Cn代表借位标志位

根据真值表可列出表达式:

Y=m1+m2+m5+m6

Cn=m3+m5

根据74151的特点,进行设计:

Y=0·m0+1·m1+1·m2+0·m3+0·m4+1·m5+1·m6+0·m7

Cn=0·m0+0·m1+0·m2+1·m3+0·m4+1·m5+0·m6+0·m7

2.3 实验要求

系统输入:逻辑电平(静态实验)、74LS197(动态实验);

系统输出:示波器;

系统功能:算术单元。

2.4 实验结果

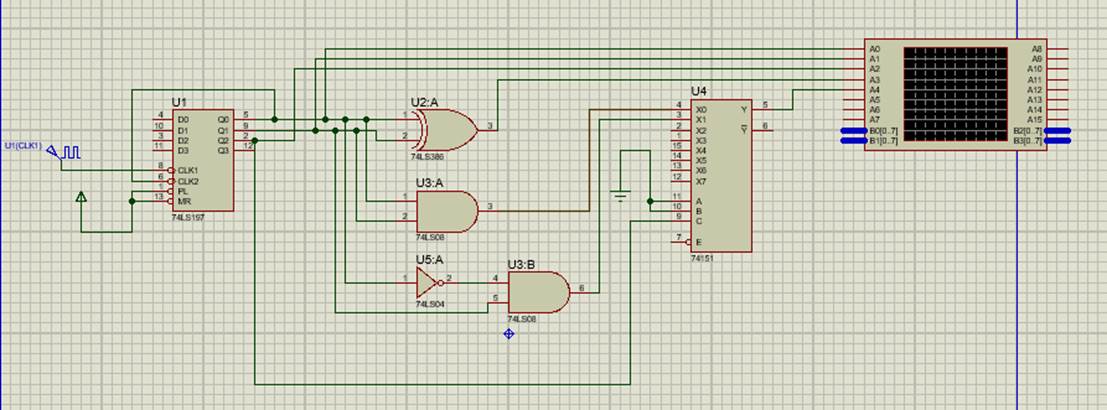

2.4.1 试验箱实验

2.4.2 试验箱连线原理图

注:由于试验箱上只有一片74151芯片,故只能使用一些逻辑门

2.4.3 proteus实验图(静态测试)

2.4.4 proteus实验图(动态测试)

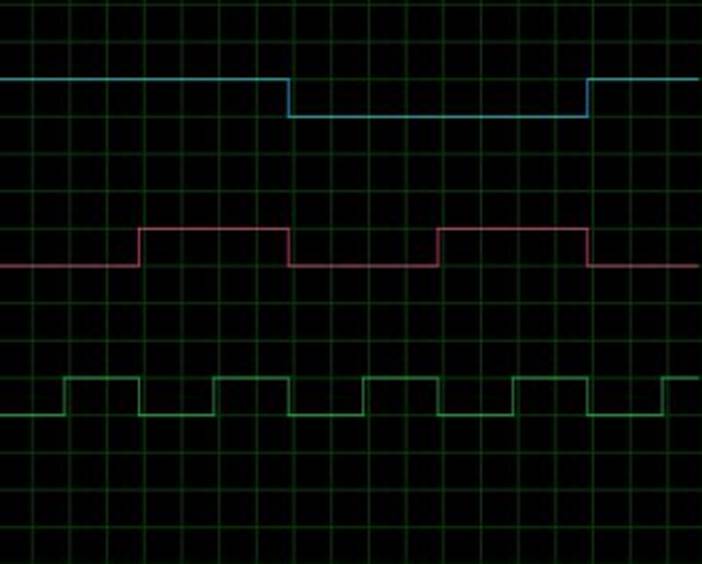

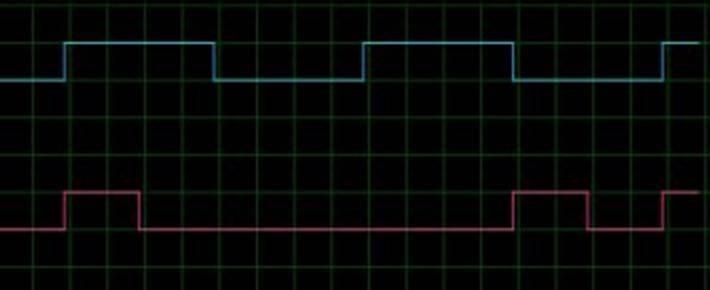

2.4.5 示波器结果

注:三条线从上到下依次是S、A、B

注:两条线从上到下依次是Y、Cn

三、逻辑单元设计

3.1 实验目的

在Proteus上,使用74HC151实现LU(LogicUnit,逻辑单元)设计。 设计一个函数发生器电路它的功能如下表3-10所示。输入为S0、S1、A、B,其中S0、S1为功能选择口。当S0、S1取0、1不同组合时,A、B进行相应的与、或、非、异或运算,输出运算结果Y。

函数发生器功能表

| 输入 | 输出 | |

|---|---|---|

| s1 | s0 | Y |

| 0 | 0 | A·B |

| 0 | 1 | A+B |

| 1 | 0 | A |

| 1 | 1 |  |

3.2 实验要求

系统输入:逻辑电平(静态实验)、74LS197(动态实验);

系统输出:示波器;

系统功能:逻辑单元。

3.3 实验思路

使用 74HC151 芯片的特点,控制端 S0 和 S1 输入为不同的二进制数的时候,Y 输出为控制端对应的八进制数输入,例如 S0=S1=0,代表八进制数 0,Y 的输出即为 X0 的输入,而我们想设计 S0=0,S1=0 代表与运算的时候,可以将 A 和 B 的与送到 x0,即可实现功能,其他函数的发生同理。

3.4 实验结果

3.4.1 实验箱连线

3.4.2 示波器结果

3.4.3 proteus实验(动态实验)

3.4.4 示波器结果